Ask an Expert

Talk to one of our experts. We can help you project savings, recommend options and plan for implementation.

What are the advantages of GaN versus Silicon?

GaN technology is superior to silicon (Si) in the creation of small power systems with more efficient power conversion. Use of GaN impacts not only the power transistor, but also overall product design and in decreasing cost around other system components including: capacitor, cooling, heat sinks, and inductors. With GaN technology, power systems are:

In which industries can the use of GaN power transistors drive significant business change?

In terms of power conversion and power efficiency, some of today’s most demanding industries including electric vehicles, data centers, renewable energy, industrial motor drives, and consumer electronics. Some of the uses of GaN semiconductors in those industries include:

Why should executives care as much about GaN technology as power system design engineers do?

GaN Systems’ approach to a new generation of power transistors using GaN technology is a major step forward in solving the persistent and universal problems of energy wasted in power conversion, along with the size limitations placed on overall product design by the ecosystem of power system components. This signals the onset of an industry-changing shift in both the short-term and ‘near future’ relationship between technology’s power systems and energy – that leads to significant individual and system-wide changes:

GaN Systems’ technology that enables power design engineers to build higher efficiency power systems today will also empower C-Suite executives and their focus on the overall competitive health of the business. Not only will GaN change a company’s relationship with energy consumption, it can change the entire trajectory of a business through the creation of whole new classes of products. This enables business to respond not only to shareholders, but to the greater good of society at large.

What is GaN Systems’ product portfolio?

GaN Systems is the only company with a product line that encompasses both the 100V and 650V product ranges needed to solve critical engineering power design challenges that exceed the capability of legacy silicon technologies in both consumer and industrial uses.

How do I purchase GaN Systems’ samples and evaluation boards?

GaN Systems has both local and global distributors to make our evaluation boards available to customers. See the “Where to Buy” portion of our website to find your distributor.

What is the best way to evaluate GaN Systems’ transistors without designing a custom PCB?

GaN Systems offers several tools to help simplify the evaluation process of GaN transistors. The boards contain all the critical components and layout for optimal switching performance, including a gate drive circuit, an on-board gate drive supply, and bypass capacitors. Refer to the “Where to Buy” portion of our website to find your local distributor, who can help supply our latest tools.

What is the recommended gate drive voltage?

+ 6/0V is recommended for the gate drive for systems in the 1.5kW and lower range. Some of our customers benefit from driving with +6/-3V in high power systems creating more noise immunity at the gate. Consult “GN001 Application Guide – Design with GaN Enhancement mode HEMT”

What is the absolute maximum gate to source voltage rating?

We specify 7.0 V as the absolute maximum DC voltage setting for the gate drive and also specify that for transient spikes, the gate can survive up to +10/-20 V. These specifications allow designers to easily use a 6.0 V gate drive setting.

Can I use 5V for the gate drive?

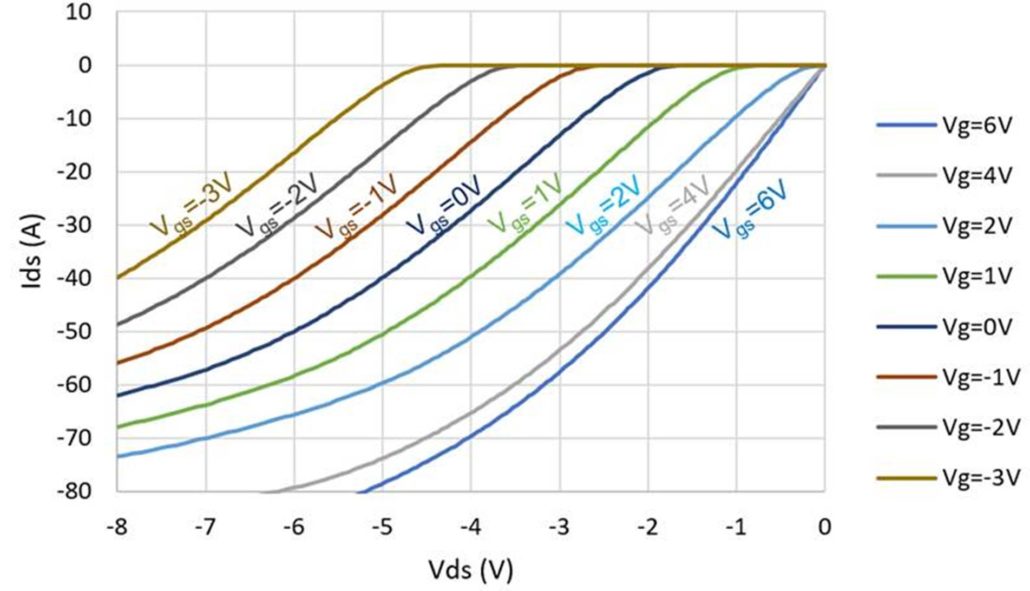

A 6 V gate drive voltage is recommended for the maximum efficiency point, where the Enhancement mode HEMT (E-HEMT) is fully enhanced and reaches its optimal efficiency point. A 5 V gate drive can be used but may result in a slightly lower operating efficiency. Gate voltage also effects maximum current. Refer to the data sheet Ids vs Vds Characteristic figures.

Do I have to use a negative gate voltage for turning it off

Not necessarily. Inherently a GaN Systems E-HEMT does NOT require a negative gate bias to turn off. Negative gate bias ensures safe operation against the voltage spike on the gate, but at the same time, it increases the reverse conduction loss. For more details, please refer to the gate driver application note “GN001 Application Guide – Design with GaN Enhancement mode HEMT”

How can I control the device slew rate?

Similar to a silicon MOSFET, the external gate resistor can be used to control the switching speed and slew rate. With Gan Systems E-HEMT devices, the slew rate is nearly linear and does dramatically increase dv/dt the way Superjunction MOSFET’s do during turn off.

What is the recommended gate resistance to start with?

It is recommended to start with a turn-on gate resistor in the range between 20Ω to 47Ω, and then adjust the resistor to achieve the desired slew rate. Lower turn-off gate resistance is recommended for better immunity to cross conduction. Please see the note “GN001 Application Guide – Design with GaN Enhancement mode HEMT” for more details.

What is the Source Sense (SS) pad and how do you use it?

The Source Sense pad is a Kelvin connection to the source. It is designed to be used by a gate drive circuit to exclude the common source inductance from the gate drive loop. To make proper use of the source sense connection, the gate drive power supply (either isolated or shared with the control circuit) ground return should be referenced to the SS pad using a star point connection. Unlike power devices that use wire bonds internally for connections, our GaNPX™ packaging utilizes no wire bonds. Our source connection is already very low inductance. Utilizing the Source Sense pad can improve drive performance but may not be necessary in all systems.

The Top-side products don’t have a Source Sense pin. Why not?

Unlike power devices that use wire bonds internally for connections, our GaNPX® packaging utilizes no wire bonds so our source connection is already very low inductance. We’ve learned that simply by using a “Source Sense” connection on the PCB to either side of our Source pad, the function can easily be implemented. Allowing customers to connect to either side of our Source pad accomplishes the function and allows layout flexibility. Utilizing the Source Sense pad can improve drive performance but may not be necessary in all systems.

Can I use a standard MOSFET gate driver?

Yes, in some applications. A standard MOSFET driver can be used as long as it supports 6 V for gate drive and its UVLO is suitable for 6 V operation. Gate drivers with low impedance and high peak current are recommended for fast switching speed. Since GaN devices deliver high performance by being able to switch at speeds often close to 100V/ns, we recommend using newer generation gate drivers that are rated for 150V/ns or higher. There are many available today on the market.

Can I save money on my gate driver?

Yes, GaN Systems E-HEMTs have significantly lower QG when compared to equally sized (RDSON) MOSFETs, so high speed can be reached with smaller and lower cost gate drivers.

Can I use a standard half bridge MOSFET/IGBT driver for high side gate drive?

Many half bridge MOSFET drivers are not compatible with 6 V gate drive for GaN Enhancement mode HEMT due to their high under-voltage lockout threshold. Also, a simple bootstrap method for high side gate drive will not be able to provide tight tolerance on the gate voltage. Therefore special care should be taken when you select and use the half bridge drivers. Alternatively, isolated drivers can be used for a high side device. Please see the gate driver application note “GN001 Application Guide – Design with GaN Enhancement mode HEMT” for more details.

The Top-side products have two gate pins. Why? Do they need to be connected on the PCB?

We’ve implemented two gate drive pins on our Top-side packages to ease the layout when paralleling devices. Both of these gate drive pins are internally connected to the gate, and only one of the two should be connected. Two gates are not designed to be used as a signal conductor. When multiple devices are used in parallel, it is NOT recommended to use dual gates to pass down the gate drive signal to the next device. Always use a wide track or a polygon on the PCB to distribute the gate drive signals to multiple devices and keep the drive loop length to each device short.

Is there any DC sinking current flowing into the gate when GaN HEMTs are entirely turned on?

No. No DC gate drive current required. Refer to the data sheet to understand the gate leakage specification. Please see the gate driver application note “GN001 Application Guide – Design with GaN Enhancement mode HEMT” for more details.

What is the temperature dependence of gate-source threshold voltage?

The GaN device exhibits a threshold voltage with a slightly positive temperature coefficient, but is quite stable in the range of 25C to +150C. This stability helps insure very good paralleling when multiple devices are used.

Do you have a design example for the gate driver?

Yes. Please see “GN001 Application Guide – Design with GaN Enhancement mode HEMT” section “Gate driver example”.

What drivers work with your parts?

The number of drivers from leading semiconductor companies continues to increase. Check with your favorite driver company, and refer to “GN001 Application Guide – Design with GaN Enhancement mode HEMT” for the latest update. You can also check with your local GaN Systems sales representative.

What is the substrate pad and how do I use it?

The substrate pin is connected to the die substrate (Silicon) and is used as a thermal pad for cooling. It is electrically disconnected from the drain and source connections on the bottom-side “P” packages. For these “P” package parts, always connect the substrate (thermal pad) to the source using copper traces on the PCB. For the Top-side packages “T” and the bottom-side packages “B”, the substrate pin is internally connected to the source pin. The substrate pin (or pad) is where the majority of the heat is generated in our GaN E-HEMT, so this should be connected (using TIM or other isolating methods) to the system cooling.

What is most effective way to cool the device?

For GSxxxxP/B products, bottom side cooling with a heat sink below the PCB and copper-filled vias underneath the device is the most effective method. Additional cooling can be achieved by heat sinks on both the top and bottom sides of the devices. Please see application note GN005 for details. GSxxxxT devices are designed to be cooled by a heat sink on top of the device. Please refer to GaN Systems website for additional methods and products to improve cooling, such as Insulated Metal Substrate (IMS) modules as well as full GaN modules and micro-modules.

What is the recommended PCB layout for optimized thermal performance?

See thermal PCB layout application note GN005. Traditional high frequency layout techniques should be practiced and are important for optimizing GaN performance. The benefit of GaNPX® is that the package is near chip-scale and allows smaller, lower inductance paths in layout.

For the bottom-side cooled packages “P” and “B”, can I attach a heat sink on the top side for cooling?

Cooling through the thermal pad is recommended as it has the best heat transfer. The top-side of the package has higher thermal resistance, but it also helps the overall thermal performance. It can be used in addition to the bottom side cooling if needed. The top-side of the device is covered by a layer of solder mask and is silkscreen printed. It has an uneven surface and is not designed to withstand high voltage or to provide safety insulation. If a heat sink is to be attached on the top, a layer of interface material with HV insulation must be added between the heat sink and the device to fill the gap and provide safety insulation.

Are the drain and source pads as thermally conductive as the thermal pad? Can thermal resistance be reduced by adding copper under drain and source pads?

Drain and source pads are not as thermally conductive as a thermal pad. Adding more copper under these two pads will reduce the packaging temperature at the edge but it only has a minor affect the total junction to ambient thermal resistance.

What’s the allowable highest operating temperature of GaN?

Our parts are specified from -55C to +150C junction temperature. Refer to the data sheet for each product’s rating.

Can the thermal pad of Top-side devices carry current?

The thermal pad of Top-side devices is connected to the source internally. However, it is not designed for carrying current. Never use the thermal pad to conduct “Source” current.

Does the GaN enhancement mode HEMT have a body diode? How do the reverse conduction characteristics compare with a silicon MOSFET?

GaN Systems Enhancement mode HEMTs do not have an intrinsic body diode, and therefore, there is zero reverse recovery charge. This is one of the many ways GaN Systems’ E-HEMTs reduce losses and EMI. The devices are naturally capable of reverse conduction and exhibit different characteristics depending on the gate voltage. At the system level, the reverse conduction capability can be an advantage compared to IGBTs and SiC devices because no anti-parallel diodes are required.

On-state (VGS = +6 V):

The reverse conduction characteristics of a GaN Systems Enhancement mode HEMT in the on-state is similar to that of a silicon MOSFET, with the IV curve symmetrical about the origin, exhibiting a channel resistance RDS(ON) similar to forward conduction.

Off-state (VGS ≤ 0 V):

The reverse characteristics in the off-state are different from silicon MOSFETs as the GaN device has no body diode. In the reverse direction, the device starts to conduct when the gate voltage in respect to the drain (VGD) exceeds the gate threshold voltage, and then the device exhibits a channel resistance. It can be modeled as a “body diode” with slightly higher VF and no reverse recovery charge.

If negative gate voltage is used in the off-state, the source-drain voltage must be higher than Vth+VGS (OFF) in order to turn the device on. Therefore, a negative gate voltage will add to the reverse voltage drop “VF” and hence increase the reverse conduction loss. To reduce losses when negative gate drive is used, we recommend using Synchronous Gate drive. See “GN001 Application Guide – Design with GaN Enhancement mode HEMT” for further information.

Does GaN Systems use Cascode technology?

No. Ours are true e-mode normally-off GaN HEMTs. Our E-HEMT device improves over Cascode technology by being easily paralleled and by having truly zero Qrr. In modules and micromodules, only our GaN devices are required, thereby creating smaller and more reliable systems.

How much safety margin does the device have above the blocking voltage rating?

The blocking voltage rating BVDS is defined by the drain leakage current. The hard (unrecoverable) breakdown voltage is typically about 30% higher than the rated BVDS, or 2x the system DC voltage in most cases. As a general practice, the maximum drain voltage should be de-rated in a similar manner as IGBTs or silicon MOSFETs. See GaN Systems’ data sheets for guaranteed voltage ratings.

Does the maximum drain-to-source voltage rating change with junction temperature?

The maximum VDS voltage has a negative temperature coefficient, implying that leakage current (in soft breakdown) will increase with temperature. However, the devices are rated to 650V over the entire specified data sheet range.

What is the absolute maximum rating for drain-to-source voltage when negative voltage is applied to the Gate?

The absolute maximum drain-to-source rating is specified on the datasheet and doesn’t change with negative gate voltage.

What is the avalanche breakdown rating?

All E-HEMT GaN transistors do not avalanche and thus do not have an avalanche breakdown rating. GaN Systems’ transistors can withstand voltages higher than the rated voltage, typically 30% higher.

Do GaN HEMTs have Qrr, Trr, or Eqrr?

GaN HEMTs do not have body diode. Therefore, Qrr, Trr and Eqrr are all equal to zero. The zero Qrr/Eqrr leads to high efficiency. Zero Trr leads to high frequency capability and low EMI.

What’s a reasonable dead time applied to GaN?

This is application-dependent. A typical GaN dead time for 650V device ranges from 50 to 100 ns. Smaller dead times in the 10-20ns can be applied for 100V devices. For soft switching, dead time needs to be chosen for achieving ZVS transition.

What’s the dv/dt of GaN HEMT?

GaN enables fast switching, so that dv/dt can be higher than 100V/ns. This is normally limited by the external circuitry. Confirm that your driver is rated for high dv/dt as well.

Do I need anti-parallel diode for reverse conduction characteristics?

There is no need to parallel body diode. 2DEG of GaN E-HEMTs can conduct in 3rd quadrant without external anti-parallel diode.

Where is the spice model data?

The spice model data is located on the individual product pages of this website.

Can I parallel the GaN devices?

Yes. GaN Enhancement mode HEMT devices have a positive temperature coefficient on-state resistance that helps = balance the current. However, special care should be taken in the driver circuit and PCB layout since the device switches at very fast speed. It is recommended to have a symmetric PCB layout and equal gate drive loop length on all parallel devices to ensure balanced dynamic current sharing. GaN Systems’ “GN004 Design considerations of paralleled GaN HEMT” application note offers detailed insight.

What is the package material?

Our proprietary GaNPX® package material is high temperature epoxy-based PCB material that is similar to FR4, but has a higher temperature rating. This allows our devices to be specified to 150°C.

How many reflow solder cycles can a device handle?

The device can handle at least 3 reflow cycles.

What is the recommended reflow temperature profile?

It is recommended to use the reflow profile in IPC/JEDEC J-STD-020 REV D.1 (March 2008)

The basic temperature profiles for Pb-free (Sn-Ag-Cu) assembly are:

For SnPb assembly, preheat to 120-150°C and use peak temperature or 235°C for reflow.

What is the switching frequency speed that can be achieved using GaN?

GaN HEMTs features very low Rdson and Coss, resulting in low conduction and switching loss. Therefore, it can operate at higher frequency than that of silicon MOSFETs. At higher frequencies, more attention to thermal design and layout is required. We have many customers using our devices from hundreds of kHz, to 13.56MHz, and even some above 50MHz.

Is EMI an issue at high frequency? Why or why not?

GaN Systems’ customers have found that EMI is improved when using GaN, compared to previous Silicon-based designs. There are several reasons for this including:

What is the maximum power level of a system in which GaN Systems’ E-HEMTs can be used?

| Our GaN E-HEMTs are well suited for high power applications such as Energy Storage Systems, Electric Vehicle On- Board Chargers, and motor drives ranging in power level from 3kW to 500kW.

– We offer the highest current GaN E-HEMTs in the industry, up to 120A today. For further detail, refer to Application Note GN004, “Design considerations of paralleled GaN HEMT” https://gansystems.com/design-center/application-notes/ |

Do GaN Systems’ E-HEMTs support the High Reliability requirements of the Aero & Defense markets?

| Yes! GaN E-HEMTs are well suited for use in the unforgiving elements of space exploration and the extreme conditions of Aero & Defense use.

For example , in the defense industry a GaN-based power system offers high efficiency and light weight, enabling battery storage systems that have better portability and longer battery run times. In critical space applications, GaN is able to withstand harsh environments that include strong magnetic forces, severe thermal gradients, intense solar radiation and high g-forces. For support dedicated to hi-rel applications, contact our valued partner Teledyne e2v |

How are MOSFETs and GaN Systems’ E-HEMTs similar? How do they differ?

Like MOSFETs, GaN Systems’ E-HEMTs are easy to drive! They are both:

Compared to MOSFETs, GaN Systems’ E-HEMTs have a:

For supporting design and layout recommendations, refer to the “PCB Layout Checklist” in Application Note GN0001. https://gansystems.com/design-center/application-notes/

Evaluate the performance of our GaN E-HEMTs directly with one of our evaluation boards. https://gansystems.com/design-center/evaluation-boards/

What is the approximate coefficient of thermal expansion (CTE) from the E-HEMT/PCB?

Die CTE

Package CTE

Can I use SnPb solder assembling your GaN E-HEMTs?

Yes, you can use SnPb solder as long as you do a proper flux cleaning.

Why are the Capacitance vs Gate Voltage (CV) measurements done at 100kHz when GaN is often used at much higher frequencies?

The CV characteristics of GaN Systems’ devices are characterized at 100kHz to minimize the parasitic effects of the test fixture when measurements are done at high frequencies such as at 1 MHz. Using this measurement technique, we are able to accurately determine the CV characteristic of our devices for a wide range of frequencies.

Why did GaN Systems introduce the new 650V low current E-HEMTs in a 5x6 mm PDFN package?

We introduced the PDFN because our customers have been asking for it! The PDFN packaging is ideal for applications that aren’t pushing the limits of switching performance but still want to benefit from the advantages that our GaN E-HEMTs offer over Si transistors. For higher volume, lower power applications, such as power adapters, motor drives in home appliances, industrial power supplies and LED lighting drivers, designers can benefit from the better switching performance (cleaner, faster, lower losses) that GaN Systems’ offers over Silicon, in a more cost conscious packaging alternative.

Can I do a direct replacement of a Silicon MOSFET PDFN with one of GaN Systems’ new PDFN E-HEMTs?

A GaN Systems’ PDFN E-HEMT is not a direct drop-in replacement for a MOSFET PDFN. First and foremost, they have different pinouts: GaN Systems’ bottom-side thermal pad is tied to SOURCE, whereas for Silicon MOSFETs, the bottom-side thermal pad is tied to the DRAIN. As well, the gate drive thresholds are different between Si MOSFETS and GaN Systems’ E-HEMTS. To take full advantage of the benefits of Gallium Nitride’s fast switching speed, refer to our FAQ section on Gate Drive as well as our library of Application Notes.

What is the EZDriveSM circuit and how can I use it?

With Gan Systems’ EZDriveSM circuit designers can use a standard, inexpensive MOSFET controller with integrated drive to drive GaN Systems’ E-HEMTS. This applies to controllers with an embedded single, dual or high-side/low-side driver. Compared to a monolithic integrated GaN transistor, the EZDriveSM circuit provides additional design flexibility for optimizing performance at a low cost. Please refer to our Application Note on the EZDriveSM circuit.

What are “pin-to-pin compatible” products?

“Pin-to-pin compatible” products are products that have same pin definition, pin function, and compatible PCB footprints. This helps engineers easily adopt and alternate products within their design without re-designing their PCB layout.

Are GS-065-060-3-x products pin-to-pin compatible to GS66516x products?

Yes, GS-065-060-3-B is pin-to-pin compatible to GS66516B, and GS-065-060-3-T is pin-to-pin compatible to GS66516T.

Are the Automotive GS-065-060-5-x-A products pin-to-pin compatible to GS66516x products?

Yes, the Automotive GS-065-060-5-B-A is pin-to-pin compatible to GS66516B, and the Automotive GS-065-060-5-T-A is pin-to-pin compatible to GS66516T.

Talk to one of our experts. We can help you project savings, recommend options and plan for implementation.