# **GN002** Application Note

# Thermal Design for GaNPX<sup>®</sup> Packaged Devices

July 20, 2021 GaN Systems Inc.

- 1. Motivation: device thermal management importance

- 2. Introduction of power loss and thermal basics

- 3. Top-cooled device thermal design consideration

- 4. Bottom-cooled device thermal design consideration

- 5. Device selection based upon thermal consideration

- 6. Power loss and thermal modeling

### **Application note outline**

### 1. Motivation: device thermal management importance

- 2. Introduction of power loss and thermal basics

- 3. Top-cooled device thermal design consideration

- 4. Bottom-cooled device thermal design consideration

- 5. Device selection based upon thermal consideration

- 6. Power loss and thermal modeling

# 1. Motivation: device thermal management importance

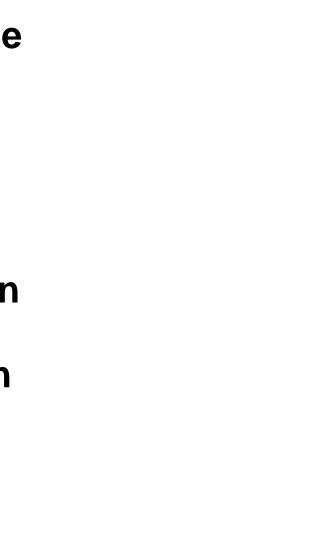

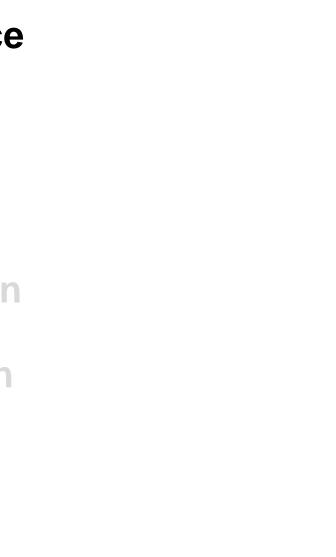

# Two electrical parameters that are dependent on temperature

1.  $R_{DS(on)}$  and conduction loss

# Gan Systems

# 1. Motivation: device thermal management importance

### **Reasons to keep device cool:**

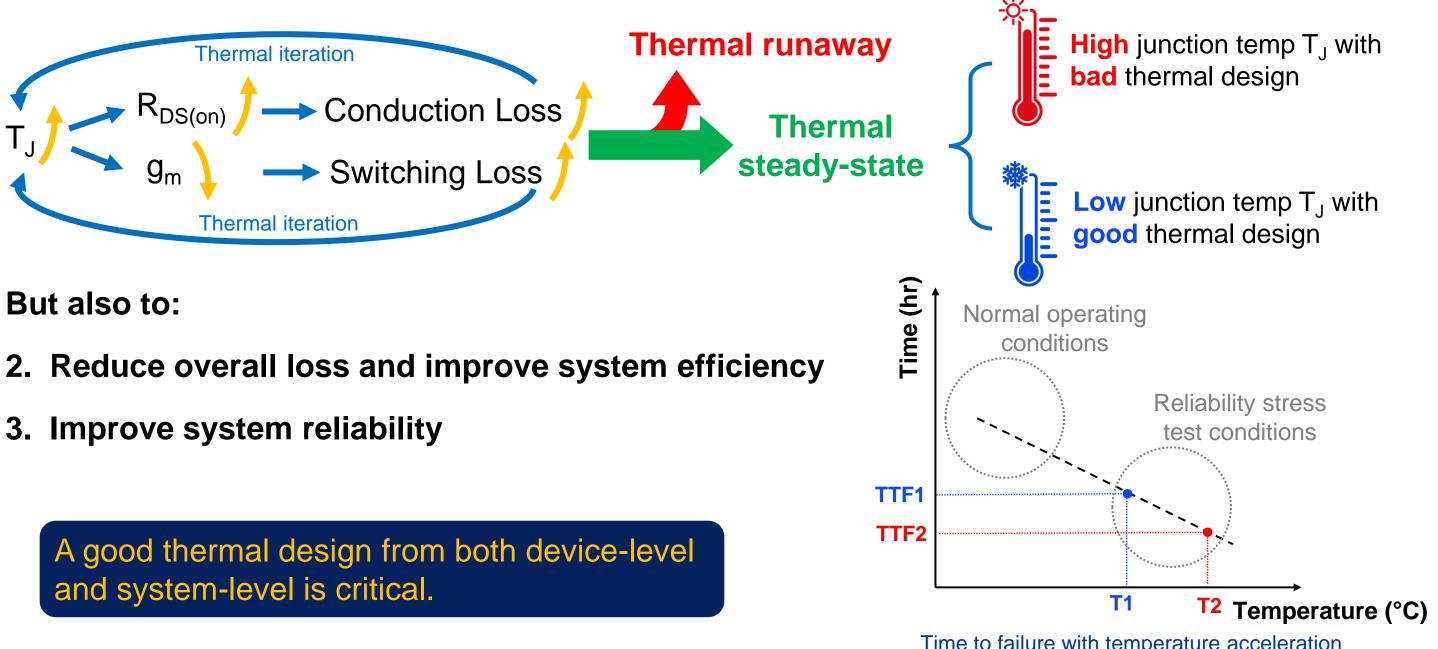

1. Prevents thermal runaway at maximum/worst operating conditions

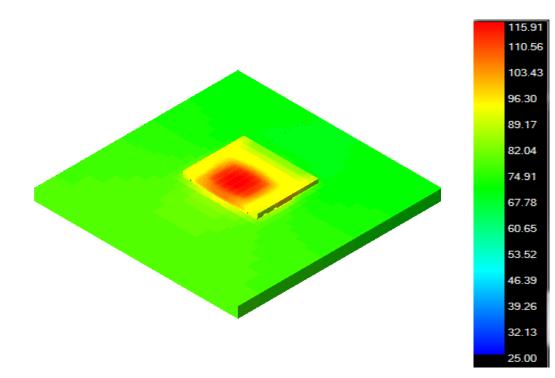

### A good thermal design also improves design power density

### **Example**:

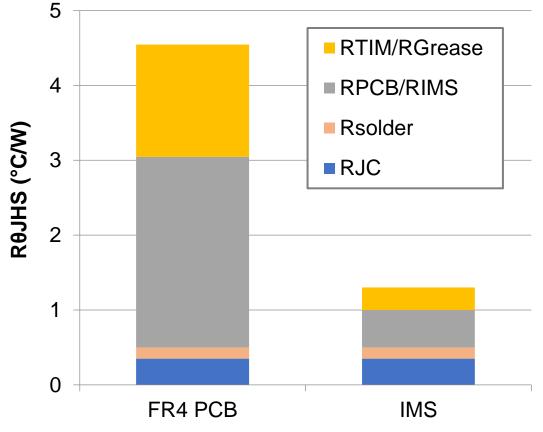

Compared to FR4 PCB heat transfer, the GaN Systems' insulated metal substrate (IMS) design reduces the heatsink volume for high-power applications

### Simulation comparison of IMS vs FR4 PCB:

- Forced-air cooling,  $T_A=25$  °C, same PCB size

- Keep  $T_J$ =100 °C. With power loss increasing, increase heatsink size to keep  $T_{\perp}$  constant.

### **1.** Motivation: device thermal management importance

### 2. Introduction of power loss and thermal basics

- Power loss 2.1

- 2.2 Heat transfer, thermal resistance, and junction temperature

- 3. Bottom-cooled device thermal design consideration

- 4. Top-cooled device thermal design consideration

- 5. Device selection based upon thermal consideration

- 6. Loss and thermal modeling

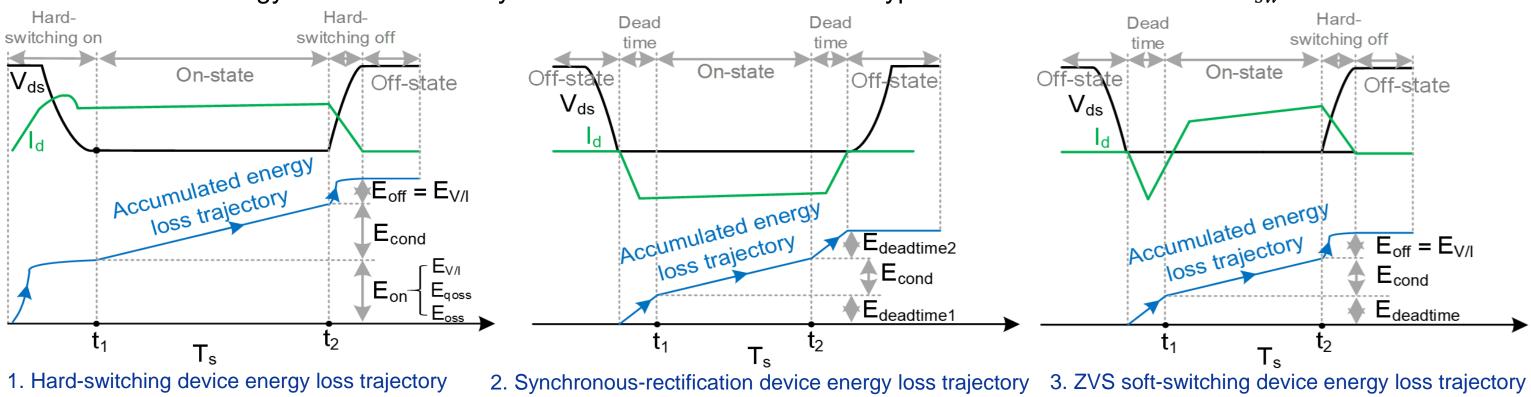

## 2.1 Introduction of power loss mechanism

Switch device's energy loss can be mainly summarized as three different types. Power loss is  $P = E \times F_{sw}$

Power loss mechanisms under various operating conditions are well understood and characterized

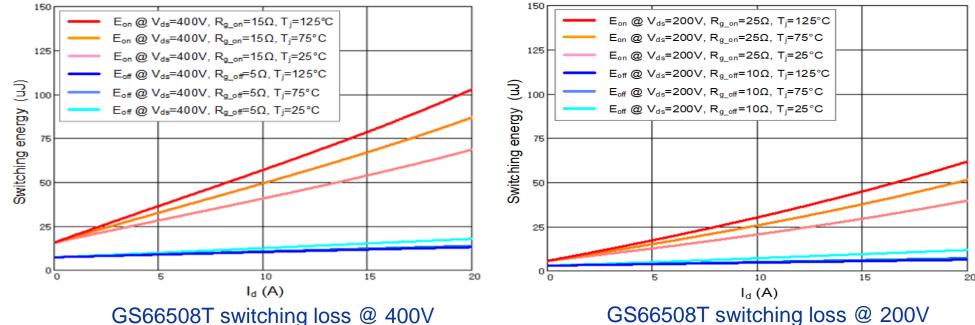

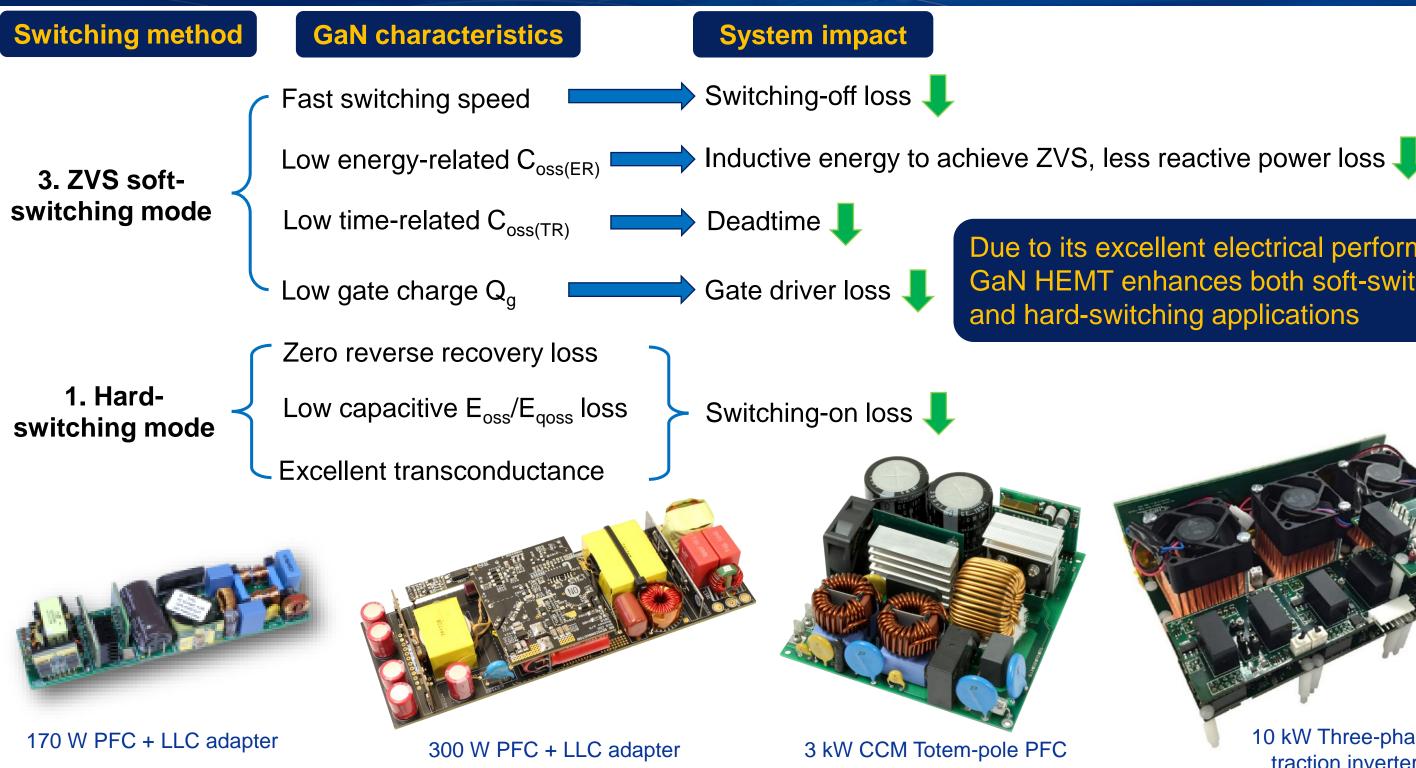

# 2.1 Introduction of power loss reduction by using GaN

# Due to its excellent electrical performance, GaN HEMT enhances both soft-switching

### 10 kW Three-phase traction inverter

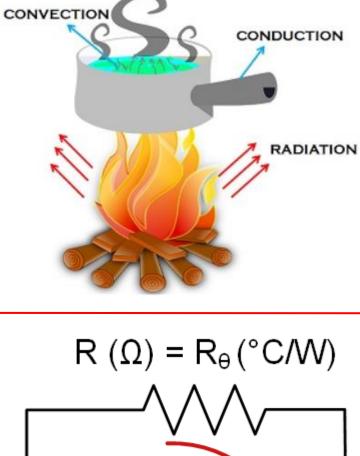

# 2.2. Heat transfer, thermal resistance, and junction temperature

Heat transfer occurs mainly in three different ways:

- **Conduction** through direct contact

- Convection through fluid movement (air is a fluid)

- **Radiation** through electromagnetic waves

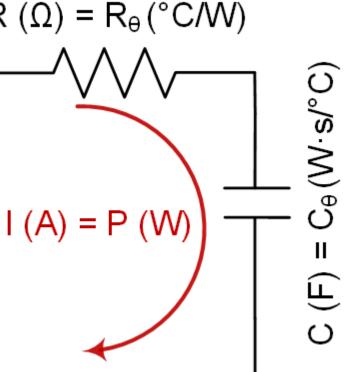

### Analogy between thermal and electrical parameters

| Thermal parameters                           | Electrical parameters |

|----------------------------------------------|-----------------------|

| Temperature T (°C)                           | Voltage V (V)         |

| Power P (W)                                  | Current I (A)         |

| Thermal resistance: R <sub>θ</sub> (°C/W)    | Resistance R (Ω)      |

| Thermal capacitance: C <sub>θ</sub> (W·s/°C) | Capacitance C (F)     |

() 0°

ΔT

Ш

$\Delta V (V)$

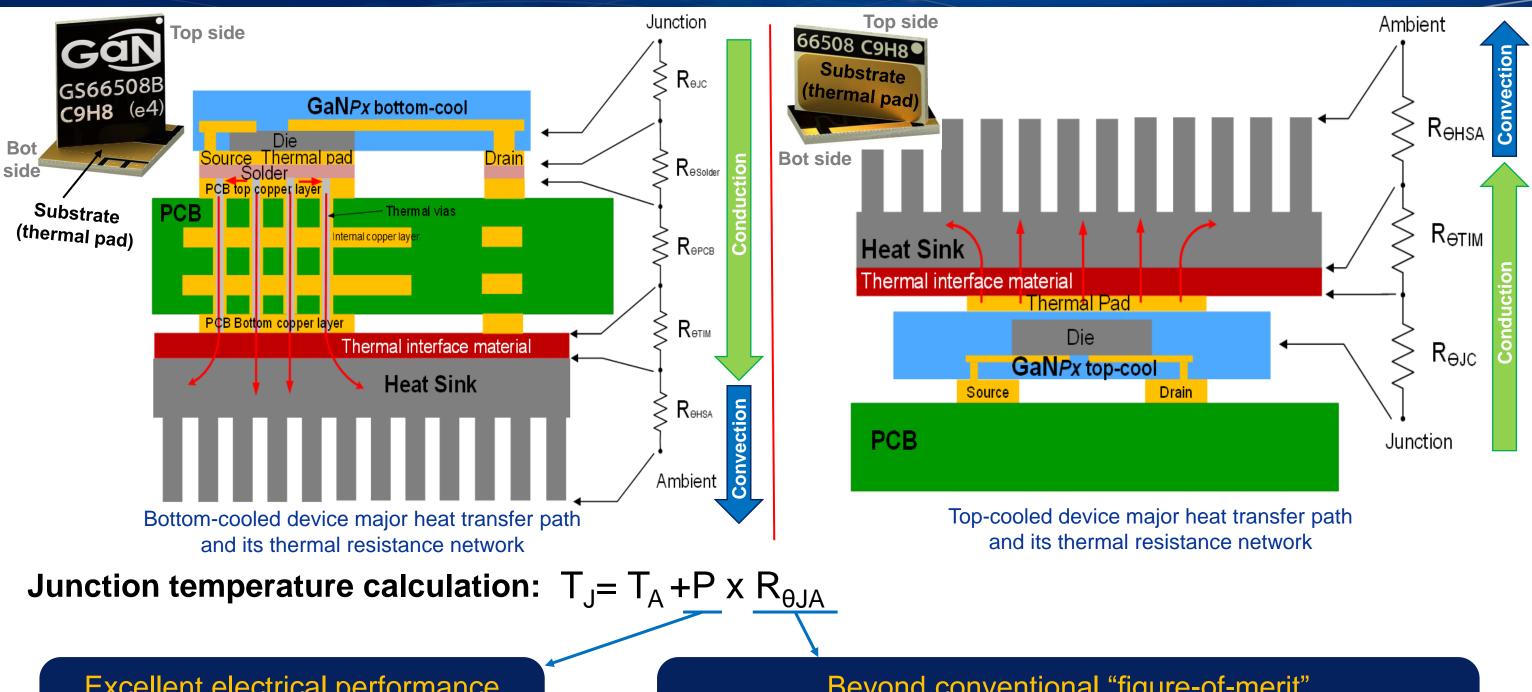

### 2.2. Heat transfer and thermal resistance on GaN

**Excellent electrical performance** (figure-of-merit) of GaN HEMTs limit the overall power loss

Beyond conventional "figure-of-merit" This presentation shows how to fully utilize GaN by thermal design to maximize the overall performance of GaN HEMTs

- **1.** Motivation: device thermal management importance

- **2.** Introduction of power loss and thermal basics

- 3. Top-cooled device thermal design consideration

- 4. Bottom-cooled device thermal design consideration

- 5. Device selection based upon thermal consideration 9

- 6. Loss and thermal modeling

Flip Chip: Low Inductance, low R<sub>ON</sub> Cu Pillars

Drain, Gate, Source on Bot (GaNPX® package)

### Device structure with GaNPX®-T package

# 3. Top-cool design – Thermal interface material (TIM) selection

### Thermal simulation operating Conditions:

• GS66516T is applied with 10 W power loss on it

| • Т <sub>НЅ</sub> = 25 °С<br>66516 с9н8● |                                           |                                                                                       | SIL-PAD K-4              | SIL-PAD 1500ST           | GAP3000S30               | HI-FLOW 300P             | GAPFILLER GS<br>3500S35-07 |

|------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|----------------------------|

| 5 (518                                   | TIM Thickness (mn                         | n)                                                                                    | 0.152                    | 0.203                    | 0.25                     | 0.102                    | 0.178                      |

|                                          | Thermal conductivity (V                   | V/m⋅K)                                                                                | 0.9                      | 1.8                      | 3.0                      | 1.6                      | 3.6                        |

| Key paramet                              | 69.20<br>66.60<br>63.83<br>61.05<br>58.28 | Thermal Resistance (°C/W)         7         7         8         7         8         1 | T <sub>J</sub> = 69.2 °C | T <sub>J</sub> = 57.4 °C | T <sub>J</sub> = 50.9 °C | T <sub>J</sub> = 46.4 °C | T <sub>J</sub> = 42.9 °C   |

| material s<br>dielectric s<br>mechanical | election: 36.09<br>strength, 33.32        | ۲<br>۵ –                                                                              | SIL-PAD K-4              | SIL-PAD 1500ST           | GAP3000S30               | HI-FLOW 300P             | Gapfiller GS<br>3500s35-07 |

| and c                                    |                                           | RTIM                                                                                  | 4.12                     | 2.94                     | 2.29                     | 1.84                     | 1.49                       |

|                                          | 25.00                                     | RJC                                                                                   | 0.35                     | 0.35                     | 0.35                     | 0.35                     | 0.35                       |

Listed TIM materials from Bergquist <a href="http://www.bergquistcompany.com/thermal\_materials/">http://www.bergquistcompany.com/thermal\_materials/</a>

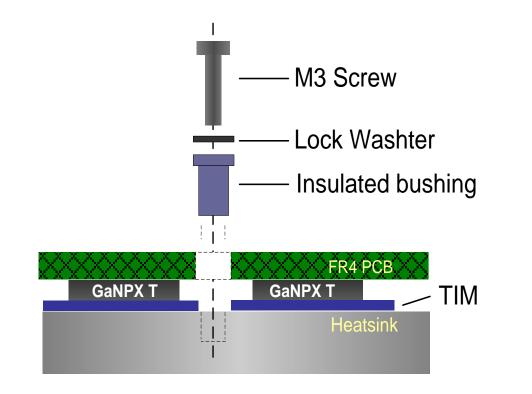

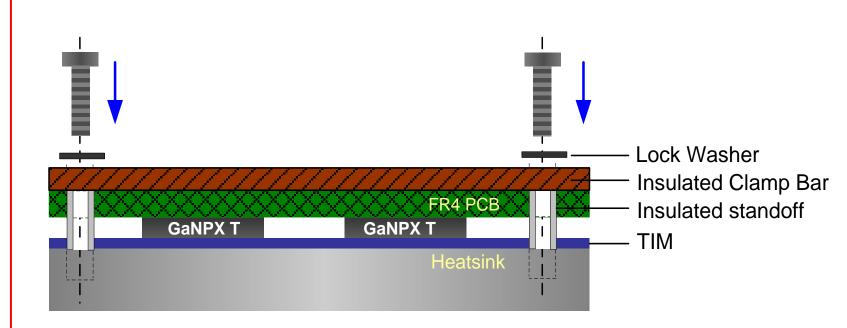

## 3. Top-cool design – Mounting consideration

### **Center mounting hole for small heatsink**

- Balanced pressure across 2 devices

- Typical recommended maximum pressure ~50psi.

- Tested up to 100psi without failure

### 2 or more mounting holes for large heatsink

- Excess PCB bending causes stress on SMD parts which should be avoided

- Locate mounting holes near to GaNPX®-T package

If warranted, use a supporting clamp bar on top of PCB

- If warranted, use a supporting clamp bar on top of PCB for additional mechanical support, not common

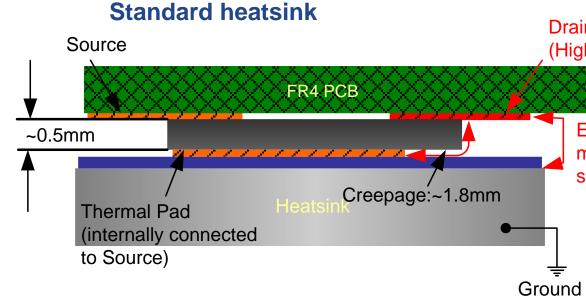

### 3. Top-cool design – Voltage isolation clearance

When using a heatsink, design to meet the regulatory creepage and clearance requirements

- Use TIM to cover Heatsink edge in areas where clearances must meet Standards

- Avoid placing Through Hole Components near GaNPX® -T package

- Use **Pedestal Heatsink** design to increase clearances and allow for placement of SMT components under the heatsink

heatsink for the placement of other SMT devices

### Drain node (High voltage)

Ensure the air gap here meets the safety clearance standards of your design

### ath the ces

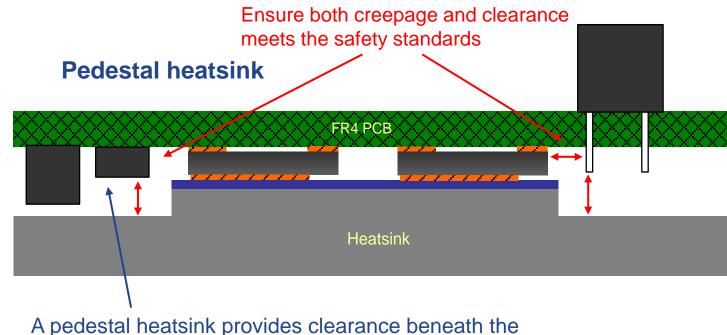

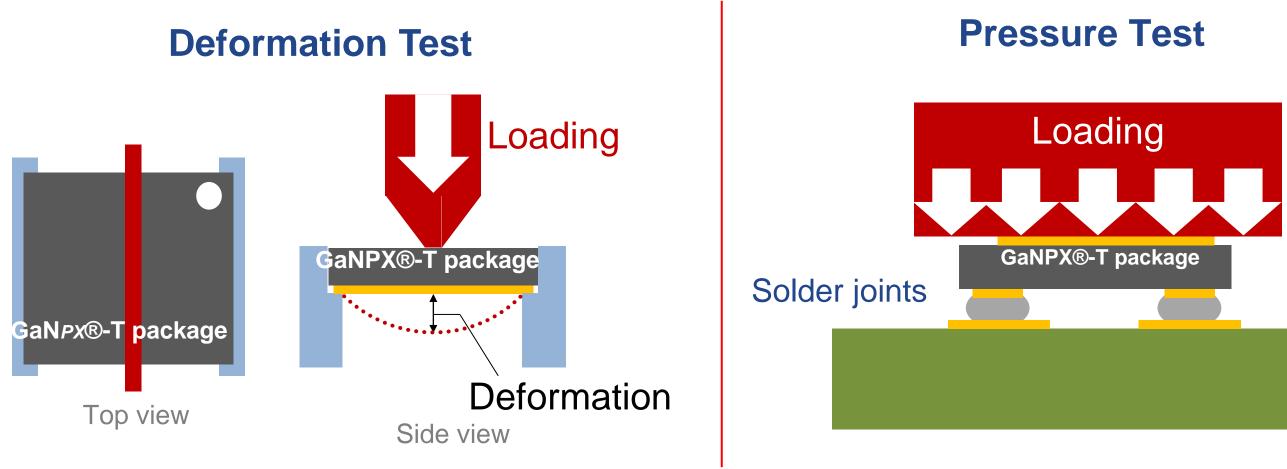

## 3. Top-cool design – Package bending pressure and deformation

| Part Number | Deformation Safe Limit (µm) | Pressure Safe Lin |

|-------------|-----------------------------|-------------------|

| GS66508T    | 50                          | 100               |

| GS66516T    | 120                         | 100               |

### mit (PSI)

### Side view

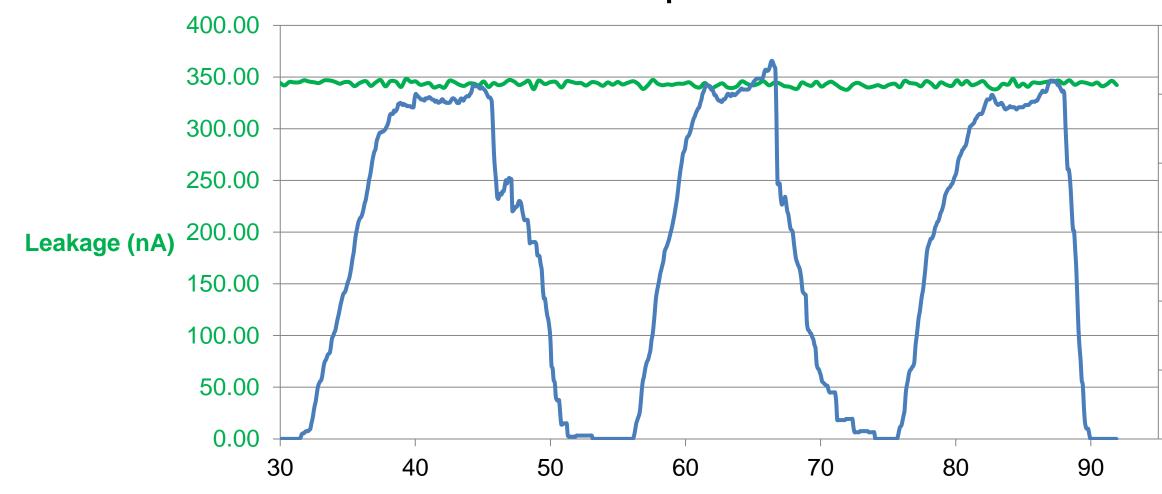

### 3. Top-cool design – Bending Pressure Test Methodology

### Example: GS66508T

DUT subject to 100 PSI over 3 pulses, with no shift in Leakage Currents 400 volts  $V_{DS}$  applied to each DUT (@ 25°C) Leakage Current =  $I_{DSS} + I_{GS} + I_{BULK}^*$  (\*Substrate)

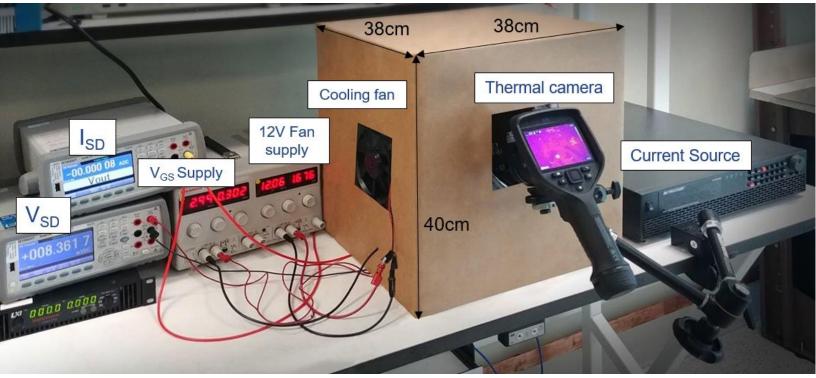

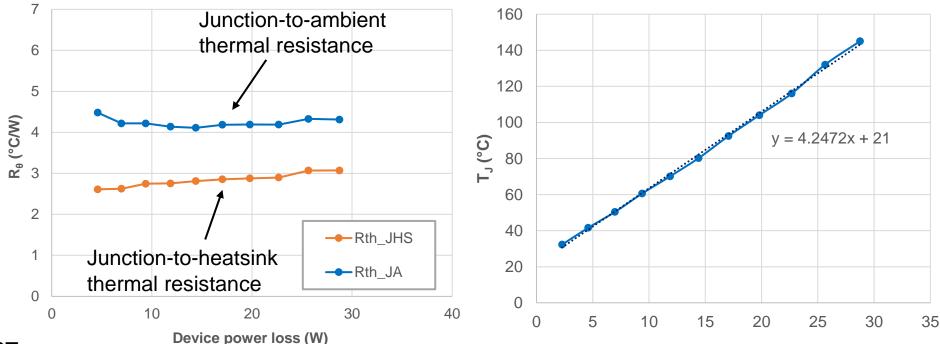

# 3. Top-cool design – Thermal resistance measurement

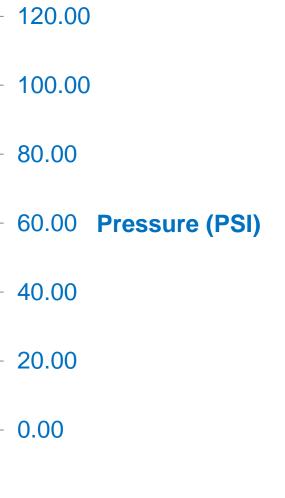

- 1. The measured  $R_{\theta JHS}$  and  $R_{\theta JA}$  for GS66516T are 3 °C/W and 4.2 °C/W, respectively.

- 2. GS66516T can dissipate 29 W loss per device.

Inside setup box region

Tested GS66516T-based evaluation board

Heat sink size: 3.4x3.4x2.5 cm<sup>3</sup>

TIM: Sil-Pad 1500ST

### Top-cool force-air cooling thermal Resistance test setup

Device power loss (W)

18

- 1. Motivation: device thermal management importance

- 2. Introduction of power loss and thermal basics

- 3. Top-cooled device thermal design consideration

### 4. Bottom-cooled device thermal design consideration

- 4.1 FR4 PCB Bottom-cool design

- 4.2 IMS Bottom-cool design

- 5. Device selection based upon thermal consideration

- 6. Loss and thermal modeling

### 4. Bottom-cooled device thermal design

### **Bottom-cooled device thermal solutions summary**

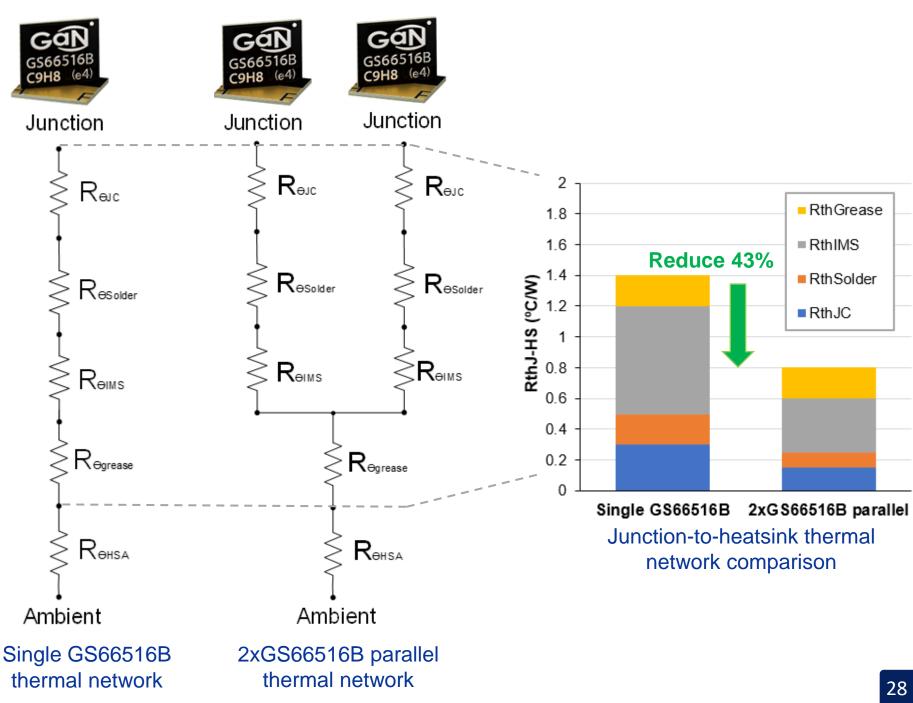

Comparison of junction-to-heatsink thermal resistance  $(R_{\theta JHS})$  based on GS66516B

FR4 PCB and IMS for bottom-cooling are both suitable solutions. Customer selection depends on design trade-off

|                       | FR4 PCB Cooling with Vias                                     | Insı |

|-----------------------|---------------------------------------------------------------|------|

| Thermal resistance    | Good                                                          |      |

| Electrical Insulation | Use TIM                                                       |      |

| Cost                  | Lowest                                                        |      |

| Advantages            | <ul><li>Standard process</li><li>Layout flexibility</li></ul> | •    |

| Design<br>challenges  | <ul> <li>High PCB thermal<br/>resistance</li> </ul>           | •    |

Performance comparison of 2 thermal design options for bottom-cool devices

### ulated Metal Substrate (IMS)

**Best**

Yes

Low

### Electrically isolated

Usually layout limited to 1 layer Parasitic inductance Coupling capacitances to the metal substrate

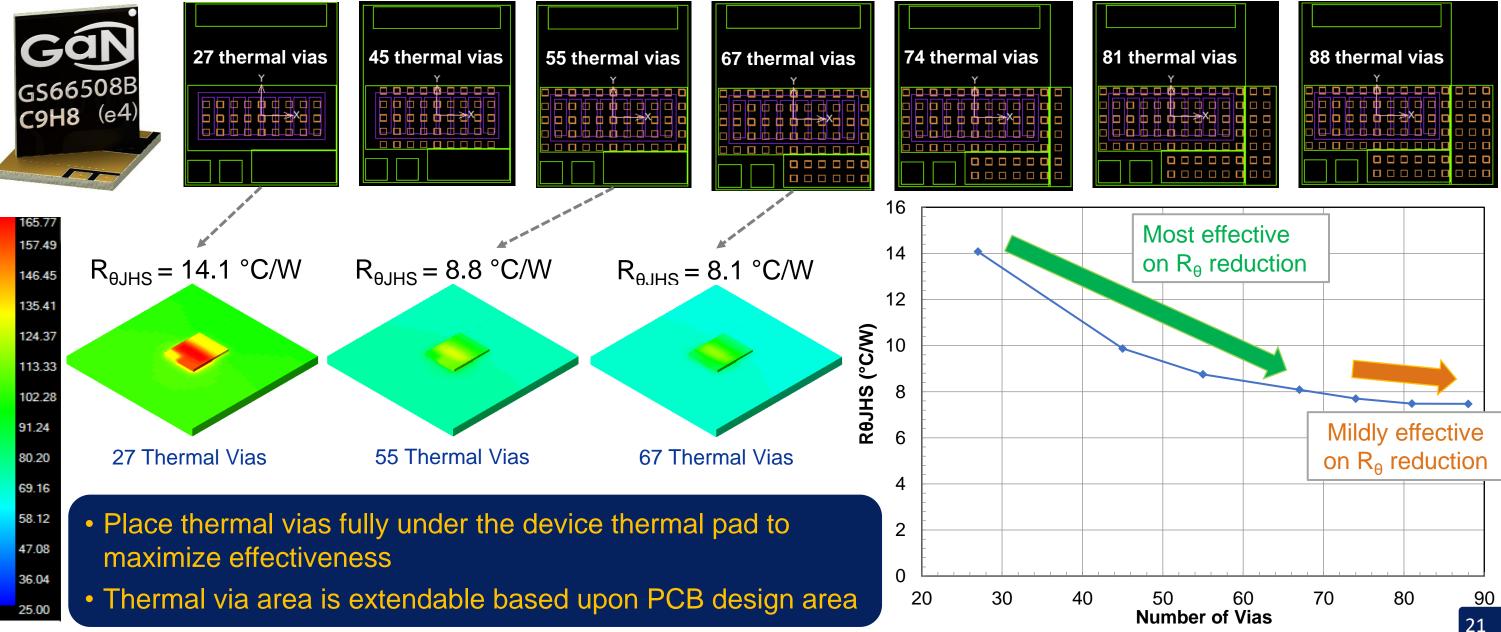

# 4.1. FR4 PCB Bottom-cool design – PCB thermal design

### Thermal vias design

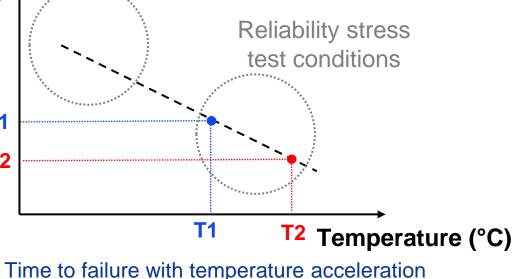

- GS66508B with device power loss 10 W. 4 layers copper with 2 oz (70  $\mu$ m) copper thickness. T<sub>HS</sub> = 25 °C

- Thermal via setup:0.3 mm diameter with 0.64 mm pitch. Standard 25 µm copper plating thickness. No via filling.

| nal vias | 88 thermal vias |

|----------|-----------------|

|          |                 |

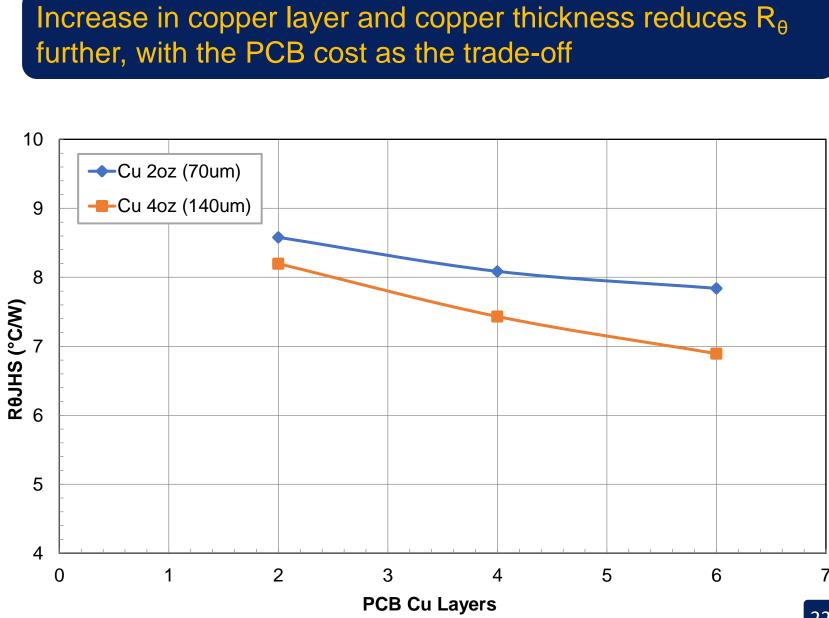

# 4.1. FR4 PCB Bottom-cool design – PCB thermal design

### Number of copper layers and copper thickness

- GS66508B with device power loss 10 W.  $T_{HS}$  = 25 °C. Overall PCB thickness keeps the same (1.6mm).

- With 55 thermal vias as example.

| PCB<br>PCB Cu Top =Thermal Pad<br>PCB Cu Top =Thermal Pad:<br>PCB Cu Top =Thermal Pad:<br>Thermal Vias<br>PCB Bottom Cu Laye 0.14 mmr<br>TIM: Sil PAD-1500ST: 0.203mm, k=1.8W/m-K |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2 layer PCB design<br>Solder: SAC350: 0.08mmk=58W/m-K<br>PCB Cu Top = Thermal Pad:<br>PCB Bottom Cu Laye 0.14 mmr.<br>TIM: Sil PAD-1500ST: 0.203mm, k=1.8W/m-K<br>Heatsink        |  |

| A layer PCB design                                                                                                                                                                |  |

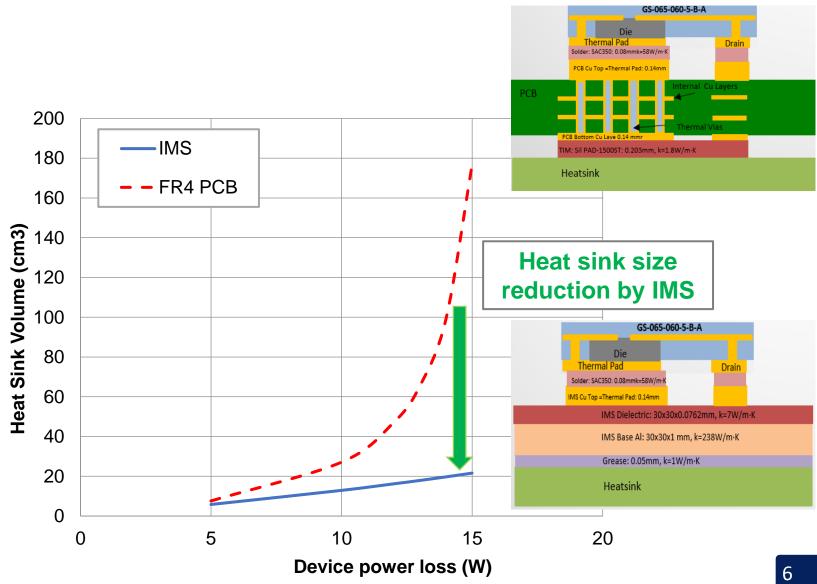

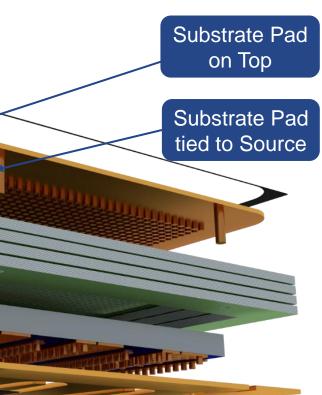

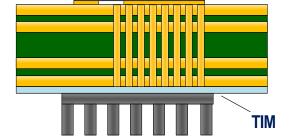

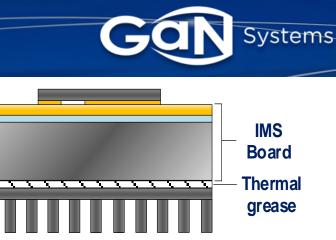

### 4.2. IMS Bottom-cool design

### **Cross section view of IMS design**

Gate driver board GaN Systems IMS design **IMS** power Heatsink board **SMT** Power Package Copper Foil: Typ. 1-4oz (35-140um) up to 10oz **Dielectric Layer: Electrical insulation** Typ. 30-200um thickness Thermal conductivity: 1-3W/mK Metal Substrate/Base

- Electrically isolated

- Aluminum or copper

IMS improves power density for high-power applications

- IMS I • Designed for high power application (3~12kW).

- Applied GaN HEMT: GS66516B single, or 2x, 4x paralleling

- IMS II • Compact. Designed for mid-high power application (1~3kW).

- Applied GaN HEMT: single GS66508B or GS66516B

# Half Bridge (650V/240A, 6mΩ)

Half Bridge (650V/30A, 50m $\Omega$ )

23

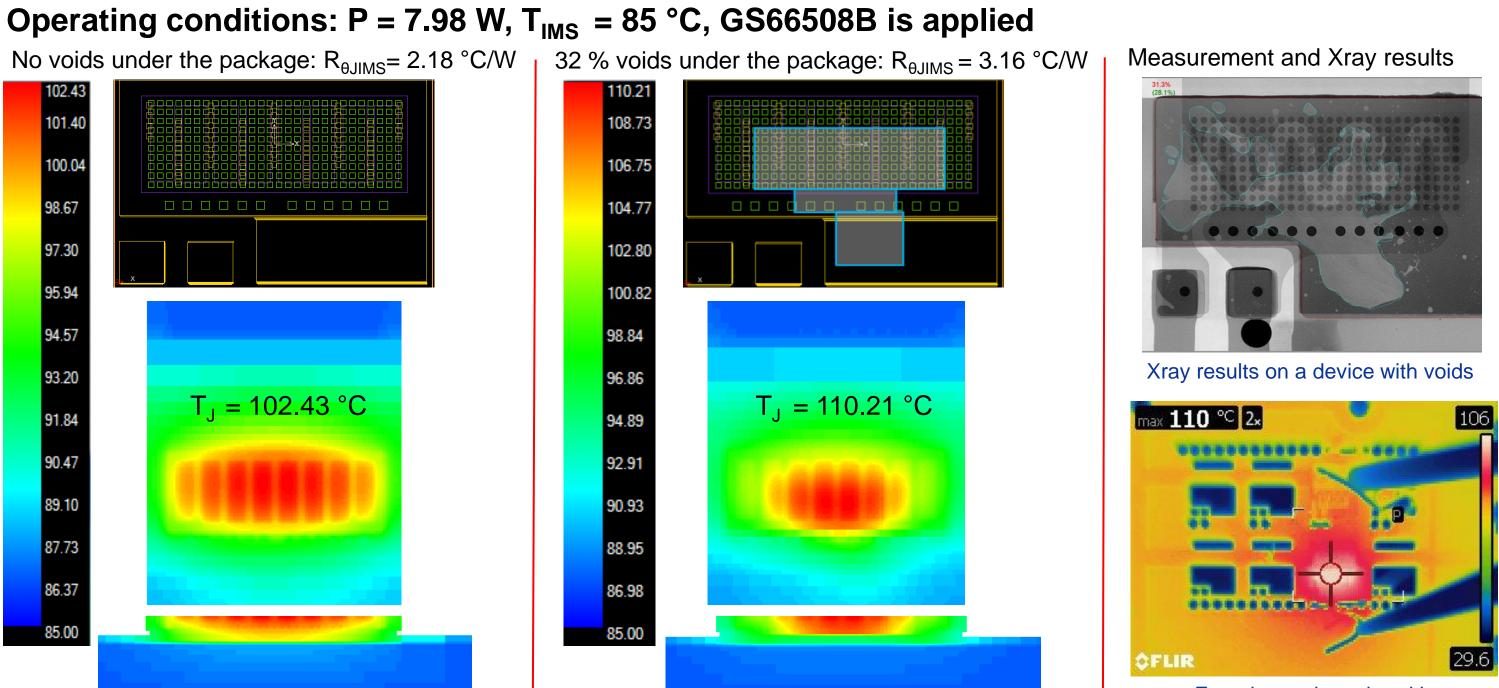

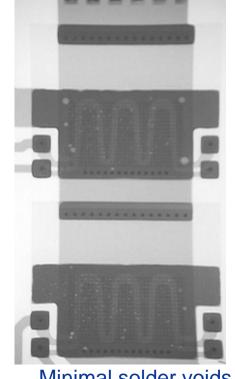

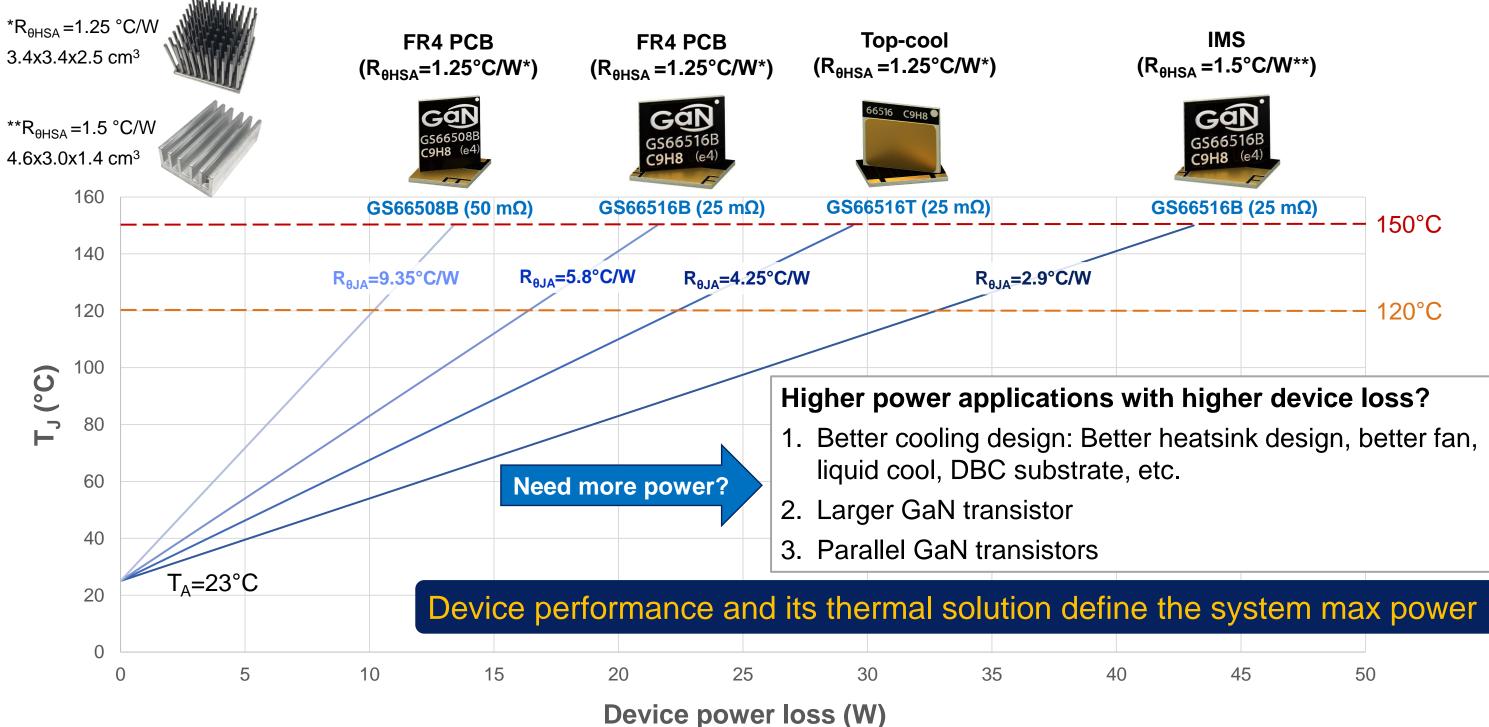

### 4.2. IMS Bottom-cool design – Solder voids consideration

### Limit voids to achieve the best IMS thermal performance

Experimental results with the device with voids

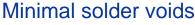

# 4.2. IMS Bottom-cool design – Thermal resistance measurement

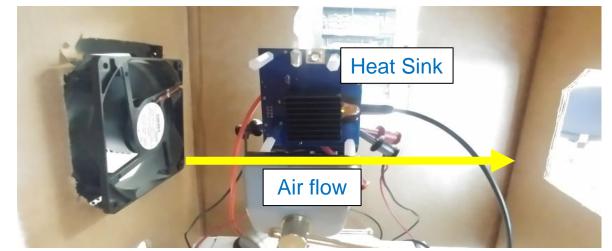

- 1. The  $R_{\theta,JA}$  for GS66516B based IMS is 2.9 °C/W.

- 2. GS66516B can dissipate 43 W loss per device.

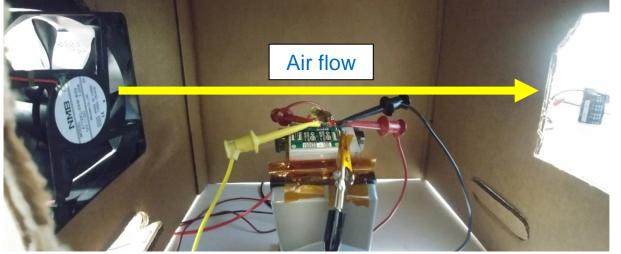

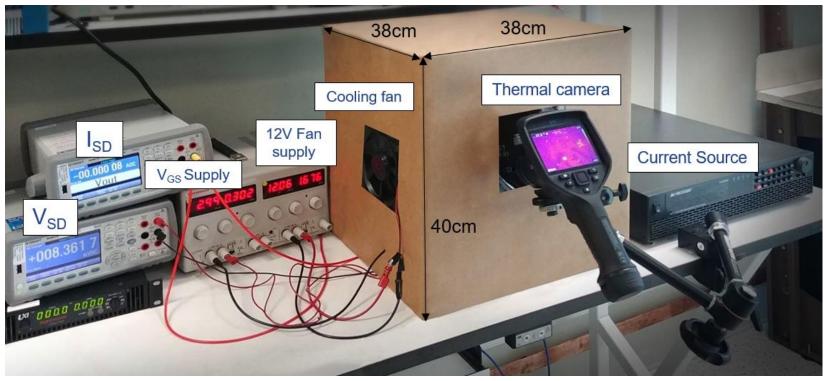

Inside setup box region

IMS force-air cooling thermal resistance test setup

Tested GS66516B-based IMS

### **Application note outline**

- **1. Motivation: device thermal management importance**

- **2. Introduction of power loss and thermal basics**

- 3. Top-cooled device thermal design consideration

- 4. Bottom-cooled device thermal design consideration

- 5. Device selection based upon thermal consideration

- 6. Loss and thermal modeling

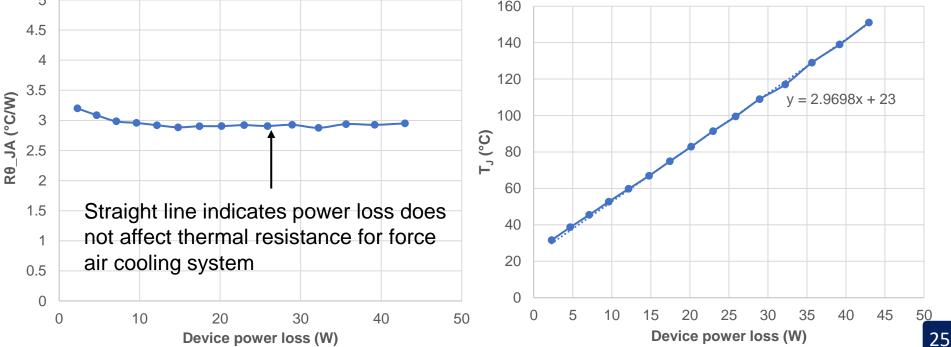

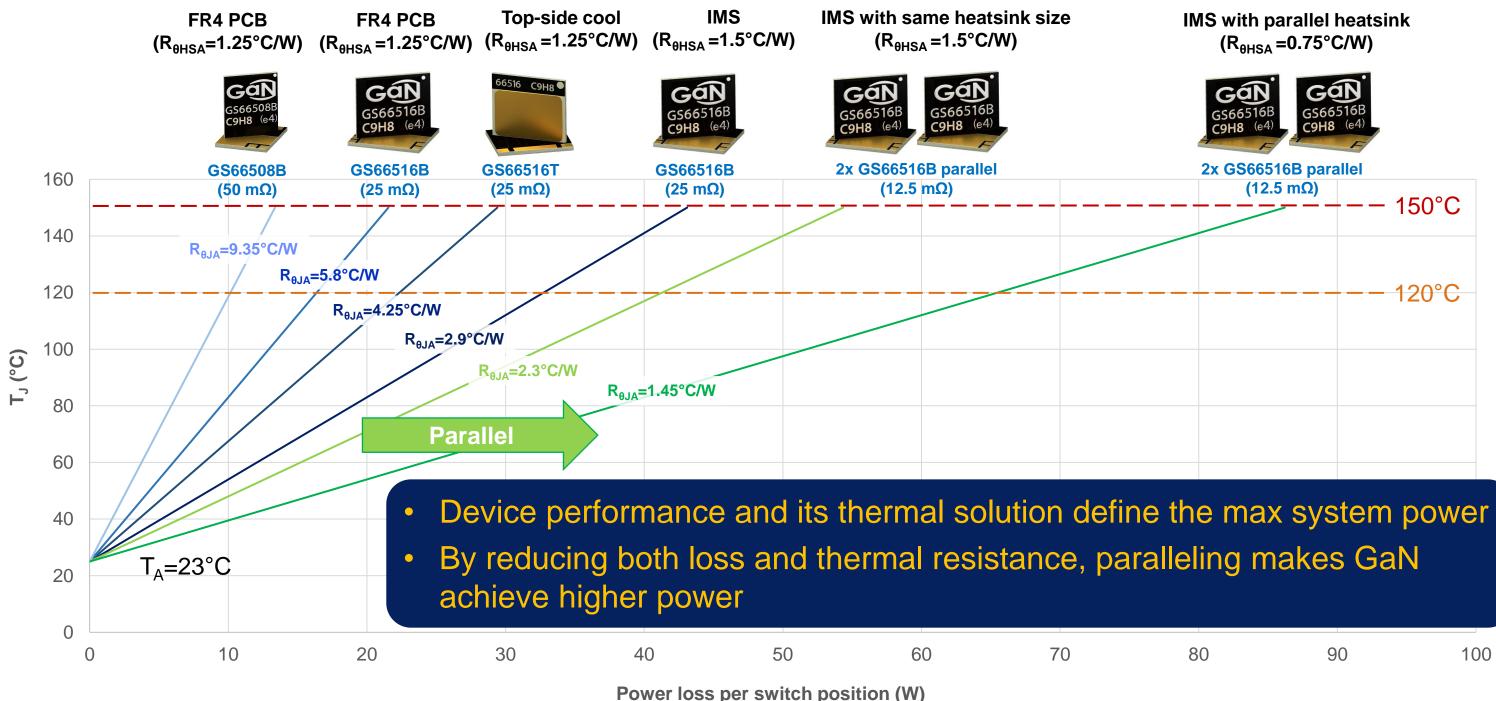

# 5. Device selection from thermal consideration – single device

Measured device power loss vs T<sub>J</sub> with different cooling methods – single discrete device solution

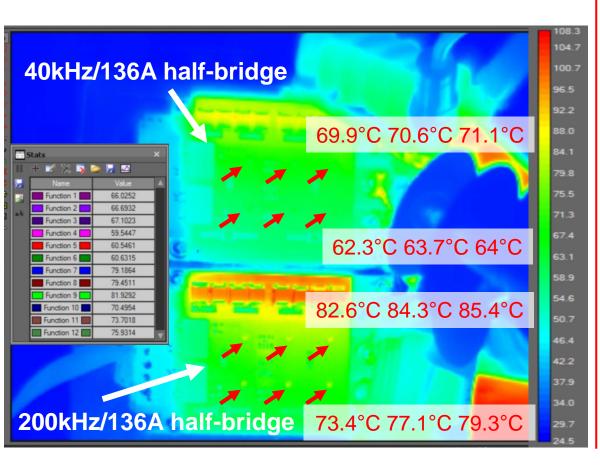

# 5.2 Enhance thermal performance by paralleling

Paralleling GaN is a proven technique to increase system power

### **Example:**

- 4xGS66516B parallel to share 136 A load current with hard-switching on/off.

- Randomly selected transistors.

- $T_{\perp}$  difference is <6 °C for the worst case.

### Paralleling reduces both system $R_{DS(on)}$ (electrical) and $R_{\theta}$ (thermal)

### 5. Device selection from thermal consideration - including parallel Gan Systems

Device loss vs T<sub>1</sub> with different cooling methods including parallel solution

# IMS with parallel heatsink

| <br>2x GS66516B para<br>(12.5 mΩ) | 150°C |

|-----------------------------------|-------|

|                                   | 120°C |

|                                   |       |

|                                   |       |

|                                   |       |

- **1.** Motivation: device thermal management importance

- **2. Introduction of power loss and thermal basics**

- 3. Top-cooled device thermal design consideration

- 4. Bottom-cooled device thermal design consideration

- 5. Device selection based upon thermal consideration

### 6. Loss modeling and thermal measurement

- SPICE modeling 6.1

- PLECS modeling 6.2

- Junction temperature measurement with thermal camera 6.3

30

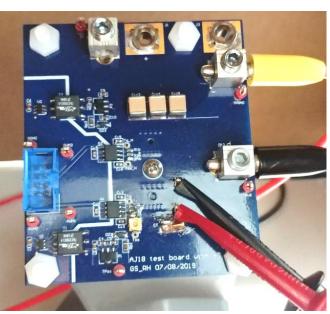

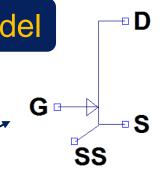

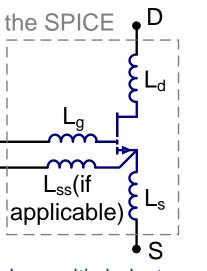

### GaN Systems provides a two-level SPICE model. For thermal modeling, use L3 model

Definitions of model levels

| Suffix | Level | Terminals                              | Description                                                                                        |

|--------|-------|----------------------------------------|----------------------------------------------------------------------------------------------------|

| _L1    | 1     | G, D, S, SS (if<br>applicable)         | General electrical simulations on application/converter level circuits. Focus on simulation speed. |

| _L3    | 3     | G, D, S, SS (if<br>applicable), Tc, Tj | In addition to L1, L3 also includes the thermal model and package stray inductance.                |

### Functions of model levels

| Functions                                   | Level 1      | Level 3      | Inside<br>model |

|---------------------------------------------|--------------|--------------|-----------------|

| IV performance as a function of temperature | $\checkmark$ | $\checkmark$ |                 |

| Voltage-dependent capacitance               | $\checkmark$ | $\checkmark$ | G               |

| Thermal model                               | ×            | $\checkmark$ | SS              |

| Package stray inductance                    | ×            | ✓            |                 |

### L1 device symbol

### L3 device symbol

Modeled parasitic inductance in L3

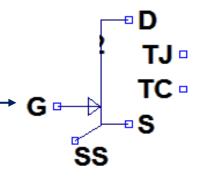

# 6.1. SPICE modeling

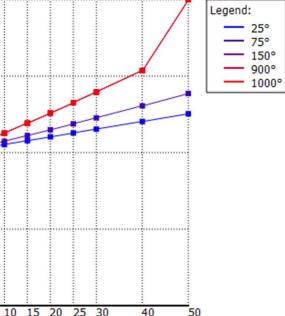

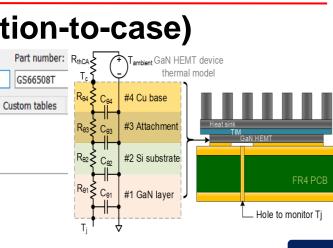

Junction-to-case thermal modeling

TJ 🖻

TC -

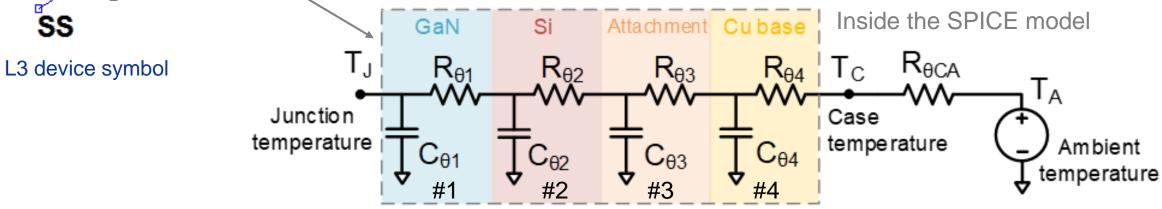

### 4-stage Cauer RC thermal model to accurately represent device

Cauer model is applied for junction-to-case thermal modeling due to:

- Unlike the Foster model (curve-fitting model), Cauer RC network is based on the 1. physical property and packaging structure

- The RC elements are assigned to the package layers 2.

### Example: GS66508B R<sub>AJC</sub> modeling

G 🗗

|    | R <sub>θ</sub> (°C/W) | C <sub>θ</sub> (W·s/°C) |

|----|-----------------------|-------------------------|

| #1 | 0.015                 | 8.0E-05                 |

| #2 | 0.23                  | 7.4E-04                 |

| #3 | 0.24                  | 6.5E-03                 |

| #4 | 0.015                 | 2.0E-03                 |

GS66508B Cauer RC model parameters

### **Rectangular Pulse Duration (s)**

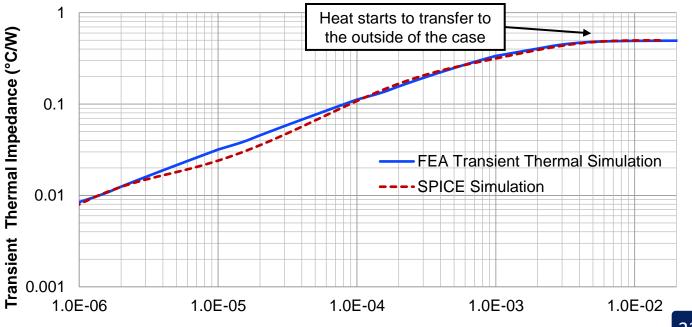

# 6.1. SPICE modeling

### T<sub>J</sub> pin can be used as an input or output, depends on the simulation purpose

### GAN SYSTEMS SWITCHING LOSS DOUBLE PULSE TEST BENCH

400V/30A Turn-on

# GON Systems

400V/30A Turn-off

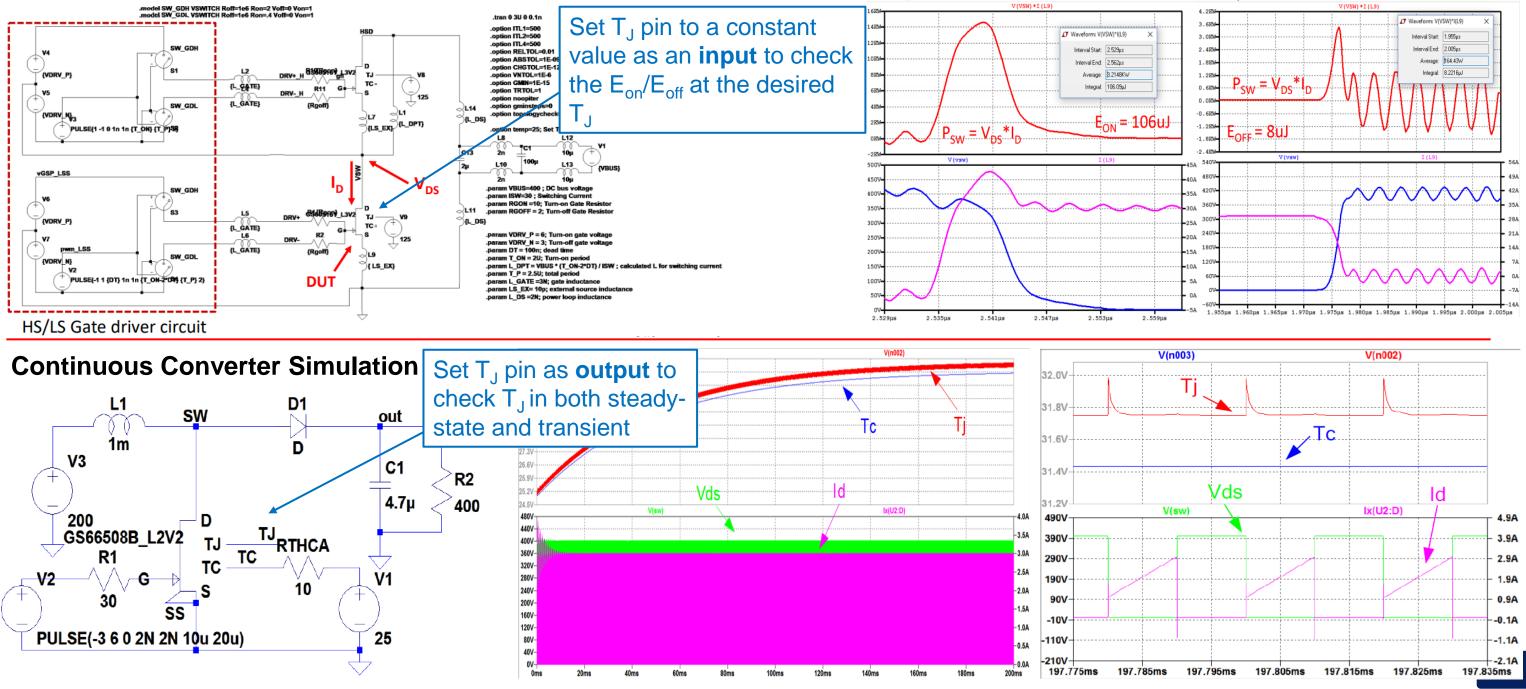

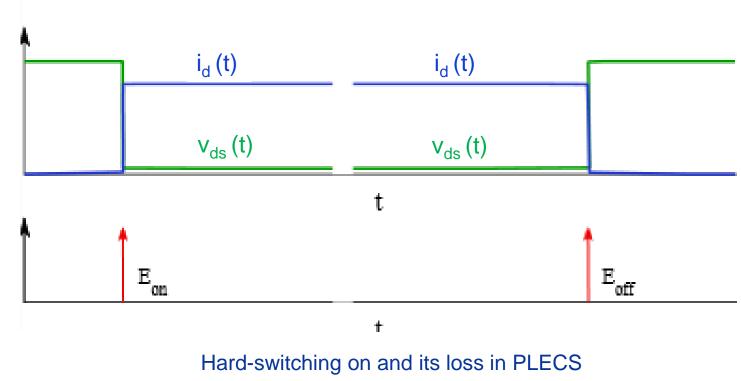

# 6.2. PLECS modeling

### **Device-level simulation** (LTspice and Pspice)

- Device characteristics ( $Q_g$ ,  $C_{oss}/C_{iss}$ , IV/CV curve,  $E_{on}/E_{off}$ )

- Simple system simulation (double-pulse test, buck, boost, etc.)

i<sub>d</sub> (t)

$v_{ds}(t)$

See parasitic effect on switching performance

### **Converter/system-level simulation** (PLECS)

- Simplify the switching transient

- Observe converter operating waveforms

- Can handle complicated device-based system-level simulation/analysis

Transient hard-switching on and its loss in SPICE

LTSPICE, PSPICE, and PLECS models assist system design to maximize performance

i<sub>d</sub> (t)

$v_{ds}(t)$

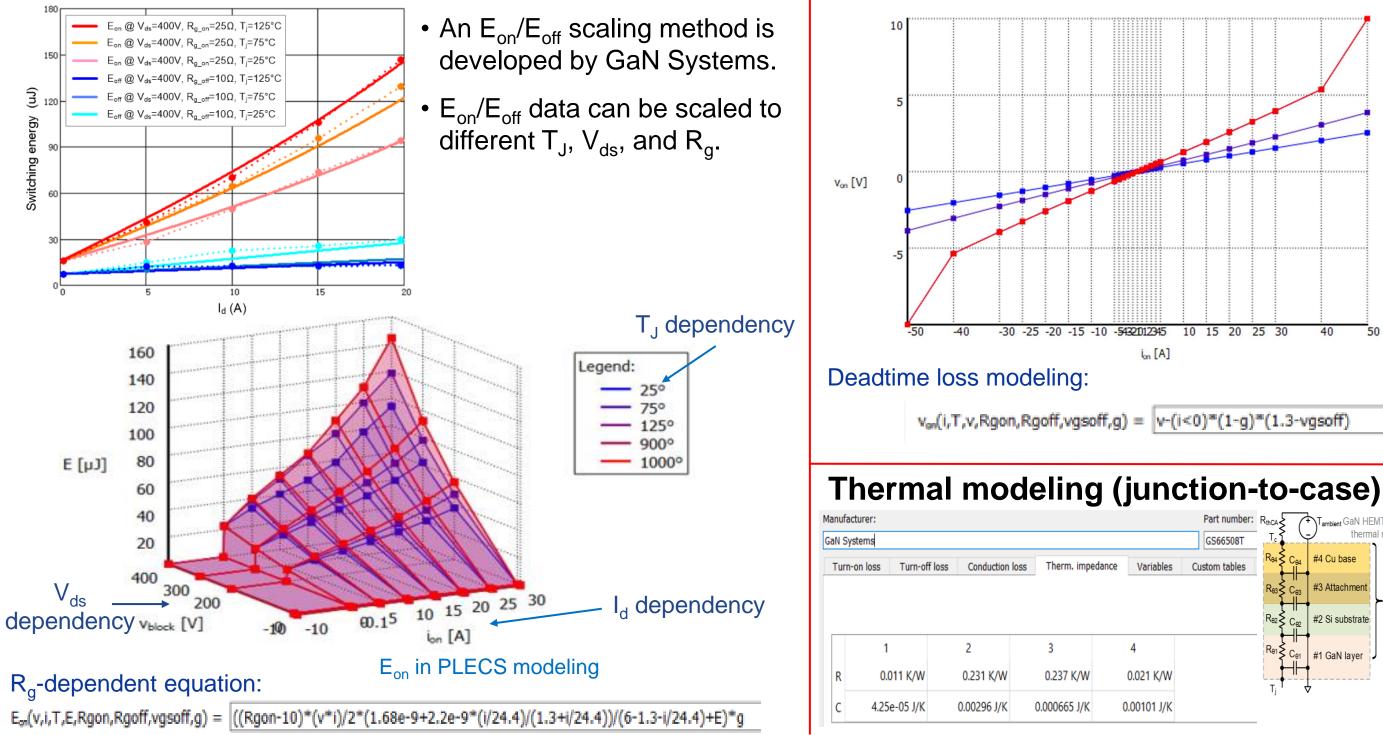

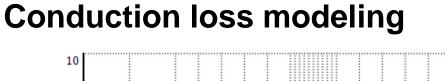

# 6.2. PLECS modeling

### Switching loss modeling

# Systems

35

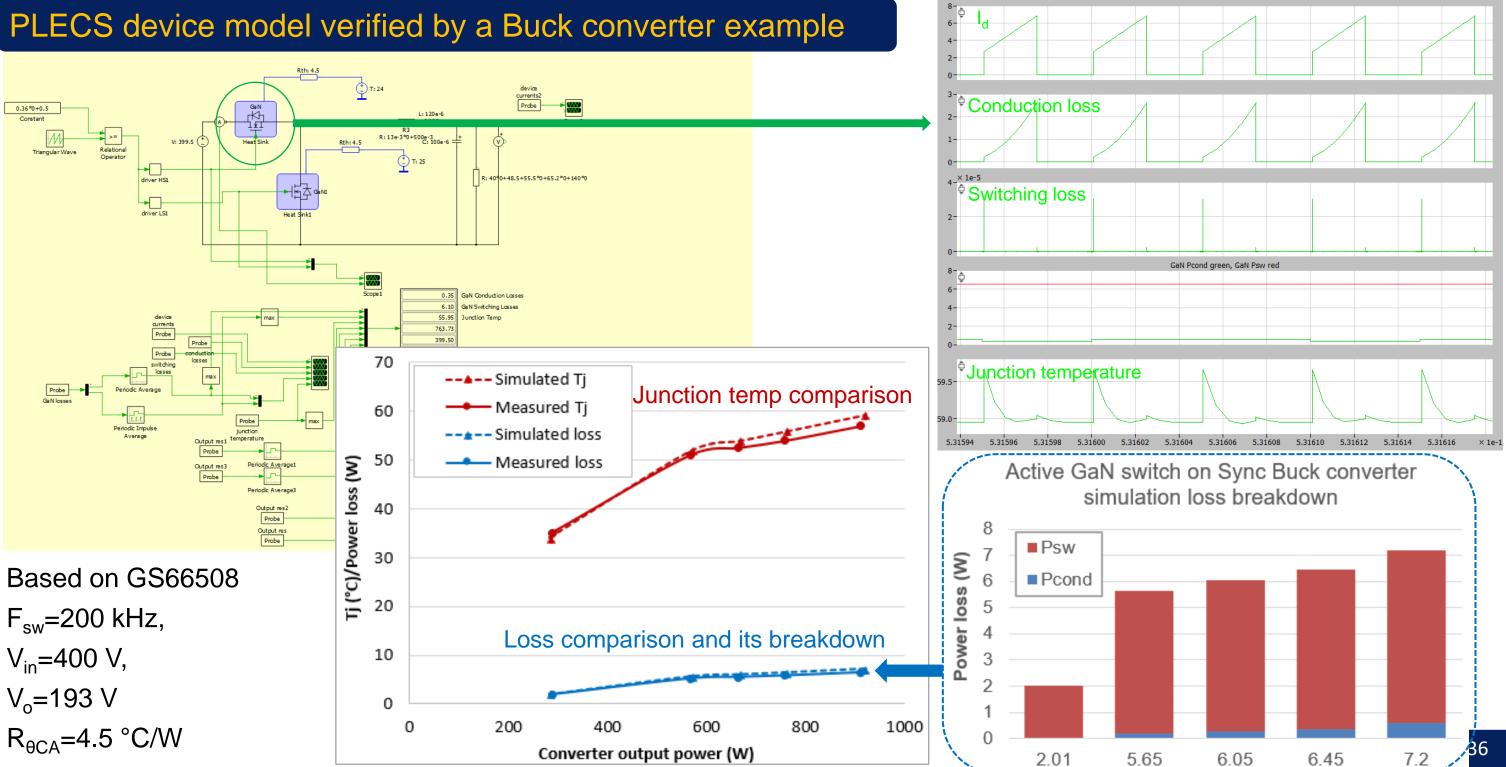

# 6.2. PLECS modeling verification

# Systems

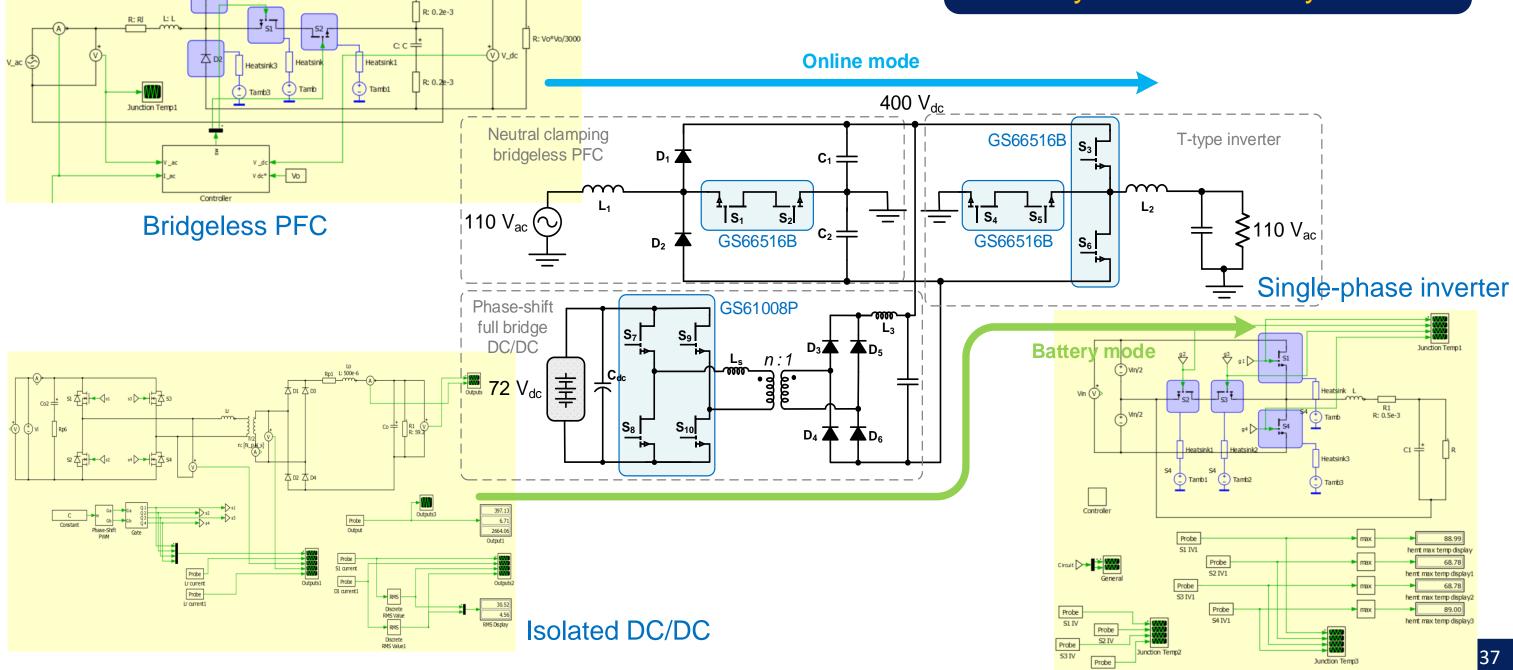

# 6.2. PLECS modeling – System loss and thermal analysis

cc∔

### **Example: UPS system**

HPFC converter

# PLECS model can be used for system-level analysis

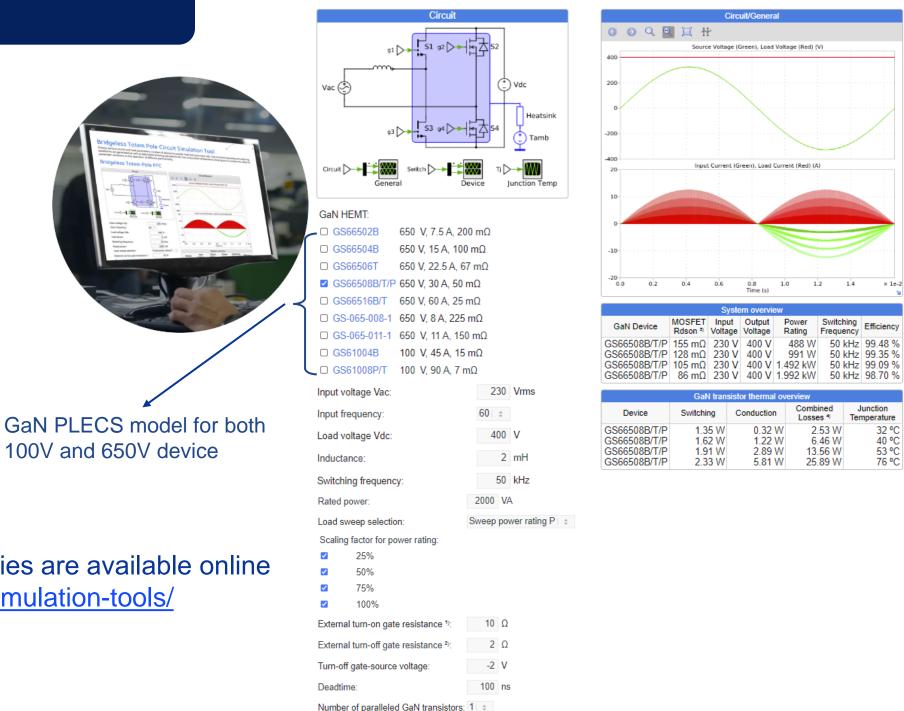

# 6.2. PLECS modeling – Online simulation tool

### GaN Systems also provide online simulation tool based on PLECS model

### Welcome to the GaN Systems Circuit **Simulation Tools**

The Circuit Simulation Tool allows you to compare application conditions by implementing specific operating values. Choose various source and load parameters, number of devices to parallel, heat sink parameters etc. Live simulated operating and switching waveforms are generated as well as data tables showing calculations for loss and junction temperature allowing you to compare the effect of parameter variations or the operation of different parts directly.

You may also download the PLECS device model files for GaN Systems' transistors.

- > BRIDGELESS TOTEM-POLE PFC

- SINGLE-PHASE, 2-LEVEL INVERTER

- SINGLE-PHASE, 3-LEVEL HALF-BRIDGE INVERTER

- > SINGLE-PHASE T-TYPE 3-LEVEL INVERTER

- ISOLATED HALF-BRIDGE LLC CONVERTER

- ISOLATED PHASE-SHIFT FULL BRIDGE CONVERTER

- > THREE-PHASE TRACTION INVERTER

- > DUAL ACTIVE BRIDGE

### All GaN Systems' device models and 8 topologies are available online https://gansystems.com/design-center/circuit-simulation-tools/

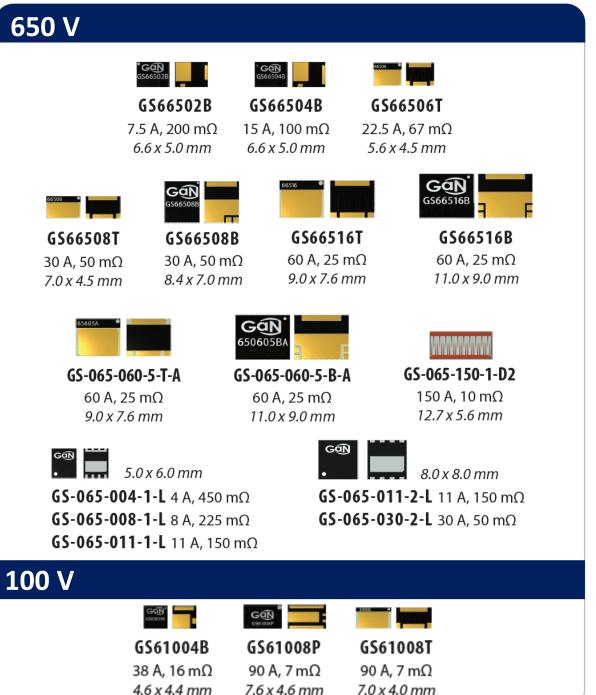

100V and 650V device

### Bridgeless Totem Pole Circuit Simulation Tool

Choose various source and load parameters, number of devices to parallel, heat sink parameters etc. Live simulated operating and switching waveforms are generated as well as data tables showing calculations for loss and junction temperature allowing you to compare the effect of parameter variations or the operation of different parts directly. You may also download the PLECS device model files for GaN Systems' transistors.

| System overview                                  |                   |                |                   |                                        |                        |                                          |

|--------------------------------------------------|-------------------|----------------|-------------------|----------------------------------------|------------------------|------------------------------------------|

| N Device                                         | MOSFET<br>Rdson ৩ |                | Output<br>Voltage | Power<br>Rating                        | Switching<br>Frequency | Efficiency                               |

| 6508B/T/P<br>6508B/T/P<br>6508B/T/P<br>6508B/T/P | 128 mΩ<br>105 mΩ  | 230 V<br>230 V | 400 V<br>400 V    | 488 W<br>991 W<br>1.492 kW<br>1.992 kW | 50 kHz<br>50 kHz       | 99.48 %<br>99.35 %<br>99.09 %<br>98.70 % |

| GaN transistor thermal overview                  |                                      |                                      |                                        |                              |  |  |

|--------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------|------------------------------|--|--|

| Device                                           | Switching                            | Conduction                           | Combined<br>Losses *)                  | Junction<br>Temperature      |  |  |

| 6508B/T/P<br>6508B/T/P<br>6508B/T/P<br>6508B/T/P | 1.35 W<br>1.62 W<br>1.91 W<br>2.33 W | 0.32 W<br>1.22 W<br>2.89 W<br>5.81 W | 2.53 W<br>6.46 W<br>13.56 W<br>25.89 W | 32 ℃<br>40 ℃<br>53 ℃<br>76 ℃ |  |  |

### 6.3. Junction temperature measurement with thermal camera

### Junction temperature measurement for GaNPX® Packaged Devices

- GaNPX<sup>®</sup> package materials are largely transparent in Long-wave Infrared (LWIR) ranges\* •

- Temperature measurement using LWIR camera is directly measuring the metal temperature inside the die, not the package surface

- In normal device operating temperature range, the delta between real junction temperature and measured package • temperature is within 1 °C.

### Junction temperature of GaNPX<sup>®</sup> packaged devices can be measured through Long-wave Infrared WIR) cameras

\* Mohanty, Akash; Srivastava, Vijay Kumar; Sastry, Pulya Umamaheswara (2014). Investigation of mechanical properties of alumina nanoparticle-loaded hybrid glass/carbon-fiber-reinforced epoxy composites. J. APPL. POLYM. SCI. 2014.

\* Pliskin, W. A.; Lehman, H. S. (1965). Structural Evaluation of Silicon Oxide Films. Journal of The Electrochemical Society, 112(10).

### **Conclusions**

- Good thermal design improves GaN transistor and system performance.

- Maximizing electrical and thermal design of GaN-based systems increases performance in softswitching to hard-switching applications and operates efficiently from several watts to many kilowatts.

### Key design tips provided in this app note

- Top-cool thermal design: TIM and heat sink mounting

- Bottom-cool thermal design: PCB design and solder voids

- Device selection including paralleling options

- Modeling tools to assist with power loss calculation and thermal design

### For more reading...

- 1. GaN Systems, GN001 Application Note: An Introduction to GaN E-HEMTs. [Online]. Available: https://gansystems.com/wpcontent/uploads/2020/04/GN001 An-Introduction-to-GaN-E-HEMTs 200416.pdf

- 2. GaN Systems, GN007 Application Note: Modeling Thermal Behavior of GaNPX® packages Using RC Thermal SPICE Models. [Online]. Available: https://gansystems.com/wp-content/uploads/2018/02/GN007-%E2%80%93-Modelling-Thermal-Behavior-of-GaNPX-packages-Using-RC-Thermal-SPICE-Models-Rev-180216.pdf

- 3. GaN Systems, GN008 Application Note: GaN Switching Loss Simulation Using LTSpice. [Online]. Available: https://gansystems.com/wpcontent/uploads/2018/05/GN008-GaN Switching Loss Simulation LTspice 20180523.pdf

- 4. GaN Systems, High Power IMS 2 Evaluation Platform Technical Manual. [Online]. Available: https://gansystems.com/wpcontent/uploads/2020/05/GSP665x-EVBIMS2 Technical-Manual Rev 200514.pdf

- 5. GaN Systems, LTspice Model User Guide. [Online]. Available: https://gansystems.com/wp-content/uploads/2018/05/LTspice-Model-User-Guide.pdf

- 6. J. Lu, R. Hou and D. Chen, "Loss Distribution among Paralleled GaN HEMTs," in Proc. 2018 IEEE ECCE, Portland, OR, 2018.

- 7. R. Hou, J. Lu, and D. Chen, "Parasitic capacitance E<sub>goss</sub> loss mechanism, calculation, and measurement in hard-switching for GaN HEMTs," in Proc. 2018 IEEE APEC, San Antonio, TX, 2018.

- 8. J. L. Lu, R. Hou and D. Chen, "Opportunities and design considerations of GaN HEMTs in ZVS applications," in Proc. 2018 IEEE APEC, San Antonio, TX, 2018.

- 9. R. Hou, J. Xu, and D. Chen, "Multivariable turn-on/turn-off switching loss scaling approach for high-voltage GaN HEMTs in a hard-switching halfbridge configuration," in Proc. 2017 IEEE WiPDA, Albuquerque, NM, 2017.

- 10. R. Hou, Y. Shen, H. Zhao, H. Hu, J. Lu and T. Long, "Power Loss Characterization and Modeling for GaN-Based Hard-Switching Half-Bridges Considering Dynamic On-State Resistance," in IEEE Transactions on Transportation Electrification, Jun. 2020. 41

# Join the wave - revolutionize your power electronics

# **Broadest line of Transistors**

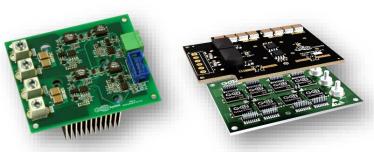

# Easy-to-Use EVBs & Reference Designs

100W PFC QR AC/DC Charger

50W Wireless **Power Amplifier**

**100W Wireless Power Amplifier**

**300W Wireless Power Amplifier**

Converter

### 250W PFC/LLC AC/DC Adapter

### 1kW Wireless **Power Amplifier**

6kW Full Bridge, **Dual Half Bridge**

14kW IMS Half Bridge

# Tomorrow's power today<sup>™</sup>

# Product and application support at gansystems.com