### Contents

- ☐ Paralleling design considerations

- ☐ Layout considerations for paralleling GaN

- ☐ Design example of 4x paralleled GaN power stage

- Experimental results

# Paralleling design considerations

### What are key considerations when paralleling power switches:

| Design parameters         | Effect on paralleling                                                                                                                                                                     | Desired                                                                                                                |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| RDS(on)                   | Affect static current sharing.                                                                                                                                                            | Positive temperature co-efficient for self-balancing                                                                   |

| Gate threshold, VGS(th)   | Impact dynamic current sharing during turn-on and off. Lower Vth results in earlier turn-on and higher switching current/loss which creates positive feedback                             | Tight distribution, temperature independent or positive temperature co-efficient                                       |

| Trans-conductance, gm     | Impact dynamic current sharing during turn-on and off.                                                                                                                                    | Tight distribution, temperature independent or negative temperature co-efficient                                       |

| Circuit design and layout | Balanced circuit layout are important for dynamic current sharing and stability of the paralleling operation. This is particularly critical for high speed power switches such as GaN/SiC | Minimize and equalize all layout parasitics to reduce circuit mismatch                                                 |

| Thermal                   | Affect the device temperature difference. Tj variation may cause dynamic or static current sharing issues depending on device characteristics.                                            | All paralleled devices should have similar thermal resistance and installed on same heatsink for good thermal balance. |

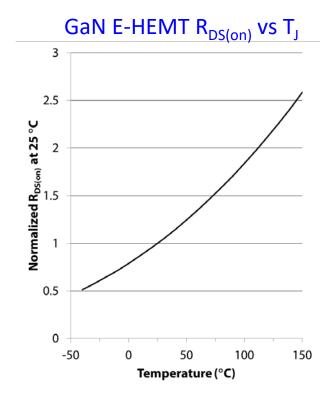

- GaN E-HEMT has positive temperature co-efficient R<sub>DS(on)</sub>

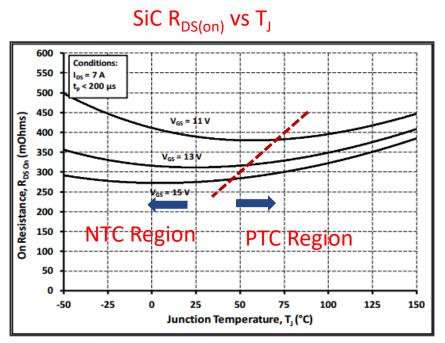

- Compared to SiC, strong temperature dependency of R<sub>DS(on)</sub> of GaN helps the current sharing in parallel operation

Figure 6. On-Resistance vs. Temperature For Various Gate Voltage

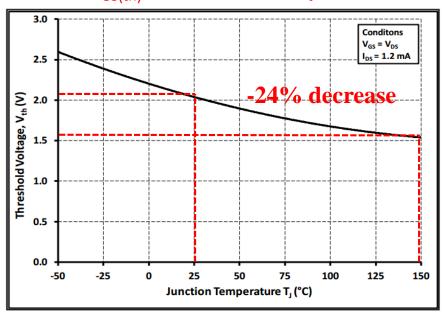

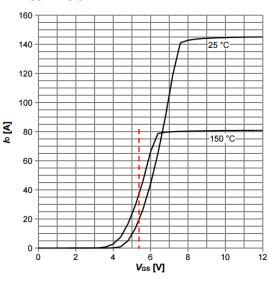

# $V_{GS(th)}$ vs $T_{J}$

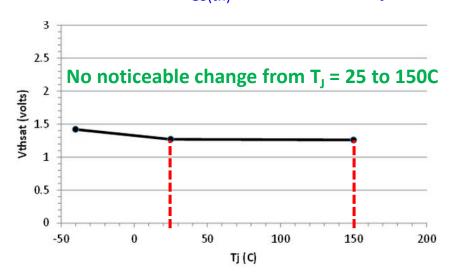

- GaN E-HEMT has stable gate threshold over the temperature range

- Si/SiC MOSFET  $V_{GS(th)}$  decreases with temperature:

- Hotter drive turn-on earlier positive feedback

### GaN E-HEMT V<sub>GS(th)</sub> is stable over T<sub>J</sub> range

## SiC V<sub>GS(th)</sub> decreases with T<sub>J</sub>

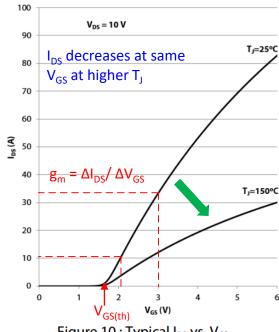

# Trans-conductance, g<sub>m</sub> vs T<sub>1</sub>

- GaN E-HEMT Trans-conductance g<sub>m</sub> decreases with temperature, good for paralleling

- This characteristics, together with stable V<sub>GS(th)</sub>, helps with dynamic current sharing and self-balancing

#### **GaN HEMT**

Figure 10: Typical I<sub>DS</sub> vs. V<sub>GS</sub>

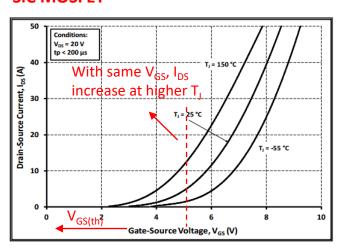

#### **SIC MOSFET**

SiC:  $V_{GS(th)}$  drops and gm slightly increases:

- Hotter device tends to have higher switching current -> higher switching loss

- Positive feedback, potential thermal runaway if not designed properly

#### SJ MOSFET

#### Si: Vth decreases and gm remain constant:

Slightly positive feedback with T,

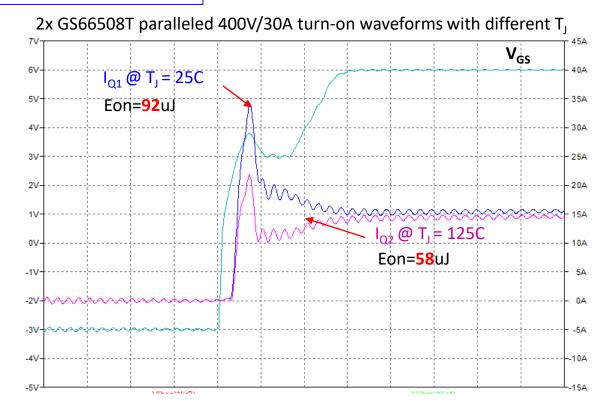

# Effect of g<sub>m</sub> on switching transient

- Negative feedback for self balancing in parallel:

- $T_1 \nearrow -g_m \searrow -I_{D@switching} \searrow -E_{on} \searrow -T_1 \searrow$

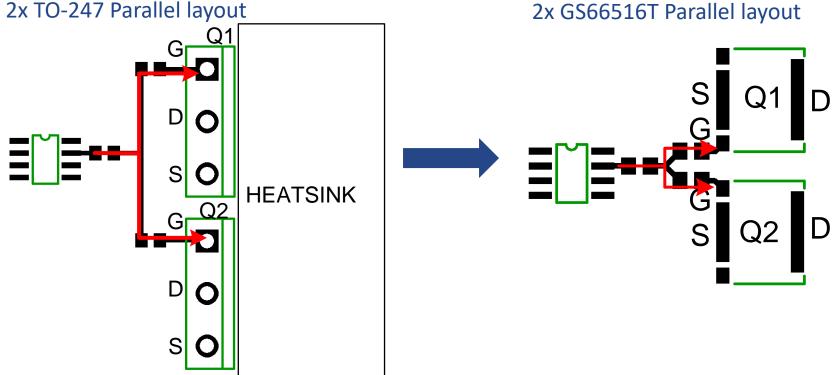

# Circuit layout - Low inductance of GaNPX® package

GaNPX® package improves the paralleling performance and stability

- Traditional package has high source inductance that impacts paralleling performance

- GaNPX® package has ultra low Ls compared to traditional package

- Top-cooled T package features symmetric dual gate pads for easier layout

GaNPX® T Package Ansys Q3D 3D modeling of GS66516T TO-247 Package inductance GS66516T (650V/25m $\Omega$ ) Drain  $= \sim 10-15$ nH Gate Top side **Bottom side** Package Source inductance Ls=0.05nH

## Circuit layout - advantages of GaNPX dual gate

- Dual gate reduces the total gate drive loop in paralleling design

- Easier to make symmetric gate drive layout

- Reduce total layout footprint area

## Key design considerations for paralleling GaN

### **Compared to other technologies:**

- GaN Systems E-HEMT characteristic is inherently good fit for paralleling as discussed.

- The R<sub>DS(on)</sub> and GaN transfer characteristics provide strong negative feedback to self balance and compensate device and circuit mismatch

- Circuit layout is most critical to GaN: Ensure successful paralleling and optimum dynamic performance.

- Therefore, this presentation will focus on gate drive and circuit layout discussion for dynamic performance of paralleling GaN:

- The impact of circuit parasitics on paralleling was analyzed

- A half bridge power stage with 4x paralleled GaN 650V/160A HEMTs was designed and validated by experimental test

### Contents

- ☐ Paralleling design considerations

- Layout considerations for paralleling GaN

- Design example of 4x paralleled GaN power stage

- **Experimental results**

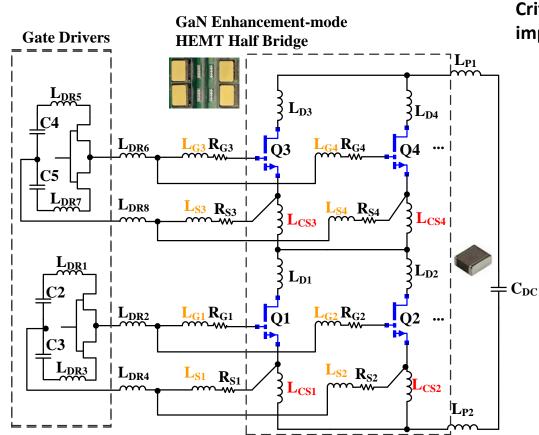

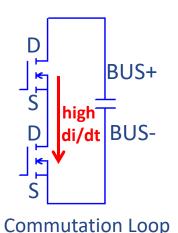

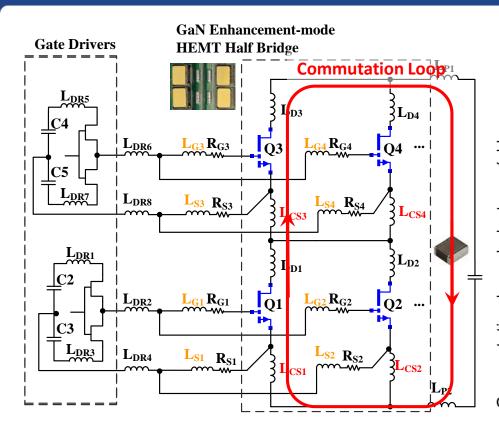

## Key layout parasitics

### Critical parasitic parameters that have high impact on GaN paralleling:

### L<sub>G1-4</sub> & L<sub>S1-4</sub>: gate/source inductance

Unbalanced L<sub>G</sub>/L<sub>S</sub> increases the gate ringing and risk of oscillation

- Equalize  $L_G/L_S$  using star connection and keep as low as possible

- Individual R<sub>G</sub>/R<sub>S</sub> is recommended to reduce gate ringing among paralleled devices

#### **L**<sub>CS1-4</sub>: Common source inductance

- Defined as any inductance that couples power loop switching noise (L\*di/dt) into the gate drive circuit

- Including the shared/common source inductance and mutual inductance between power and drive loops

- Feedback switching di/dt to V<sub>GS</sub>, impact gate drive stability and performance

- Minimize as much as possible.

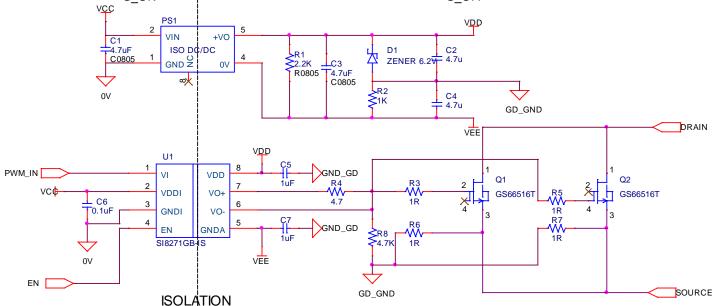

### Gate drive design for paralleled GaN

- For high current paralleling design, a small negative gate drive turn-off bias is recommended for lower turn-off loss and more robust gate drive. Recommend to use -3V to -5V with synchronous driving for optimum efficiency.

- Create bipolar gate drive from single power supply using a 6.2V Zener. Negative gate drive bias (VEE) is defined by PS1 output – Vzener(6V)

- Use small values (1-2 $\Omega$ ) for distributed gate and source resistance: R3/R5 and R6/R7

- Total turn-on  $R_{G ON} = R4 + R3(R5) + R6(R7)$ . Turn off  $R_{G OFF} = R3(R5) + R6(R7)$

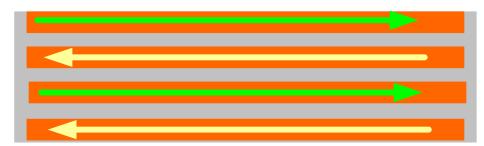

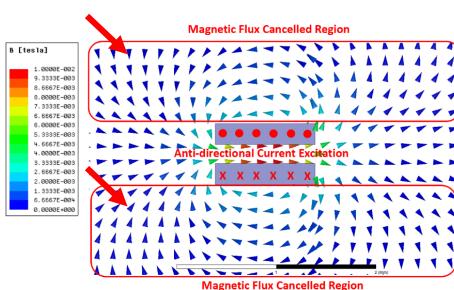

### Flux cancelling for lower inductance

- When two adjacent conductors are located close with opposite current direction, magnetic flux generated by two current flows will cancel each other in the region highlighted.

- This magnetic flux canceling effect can lower the parasitic inductance.

- Arrange the layout so that high-frequency current flows in opposite direction on two adjacent PCB layers

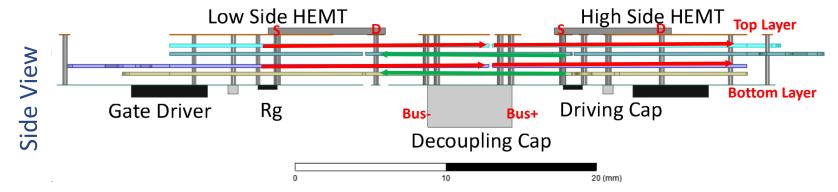

## Flux Cancelling Design for half bridge layout

### High Frequency Current alternates direction on Each Layer to provide flux canceling effect

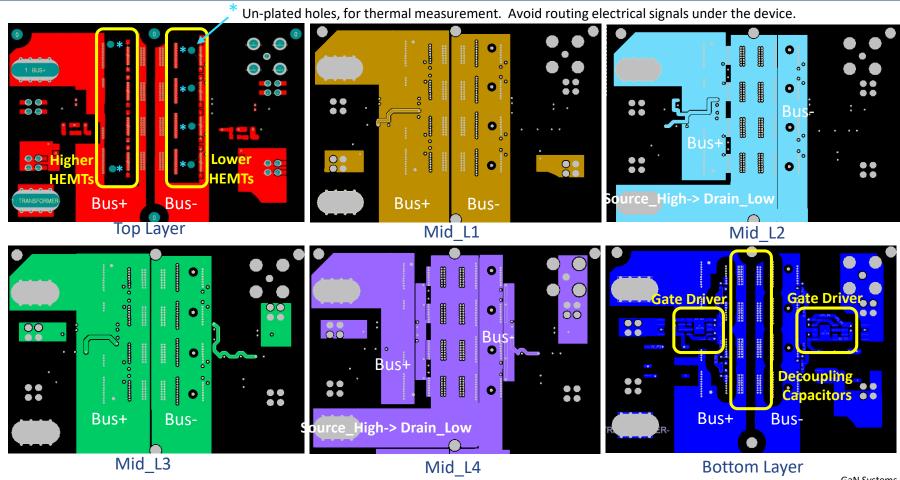

```

Top Layer: place GaN HEMTs

Mid L1: BUS+ -> Drain High; Source Low -> BUS-

Mid L2: Source High -> Drain Low

Mid L3: BUS+ -> Drain High; Source Low -> BUS-

Mid L4: Source High -> Drain Low

Bottom Layer: place Gate Driver Circuit and Decoupling Caps

```

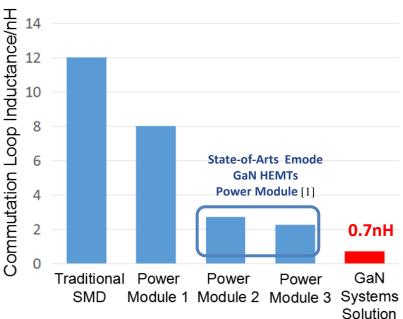

## Comparison with Benchmark

GaN Systems Solution: only 25% L<sub>loop</sub> of the Best Counterparts:

- Low inductance GaNPX® package

- Flux cancelling PCB design

### Contents

- ☐ Paralleling design considerations

- Layout considerations for paralleling GaN

- Design example of 4x paralleled GaN power stage

- **Experimental results**

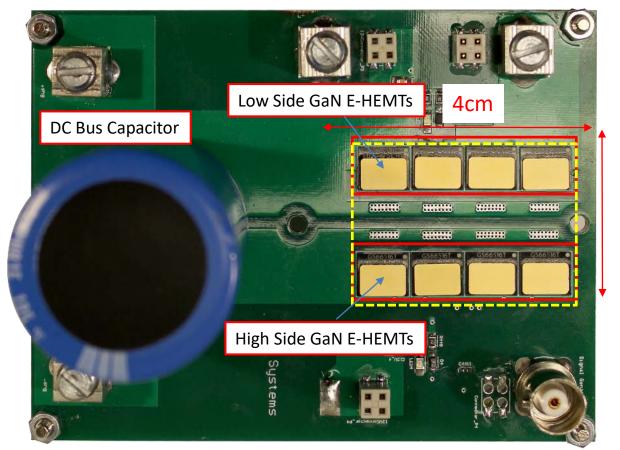

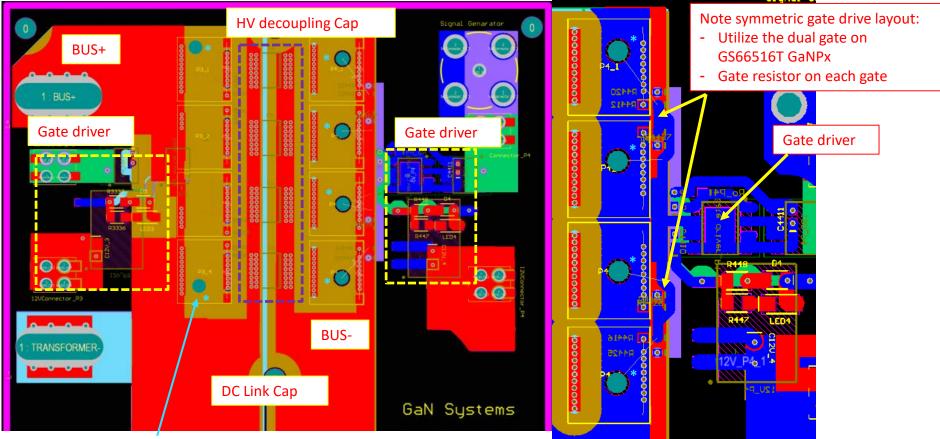

# 4x GS66516T Paralleling Test Board – Top View

### 650V/240A high Power stage design using discrete GaN EHEMTs

3cm

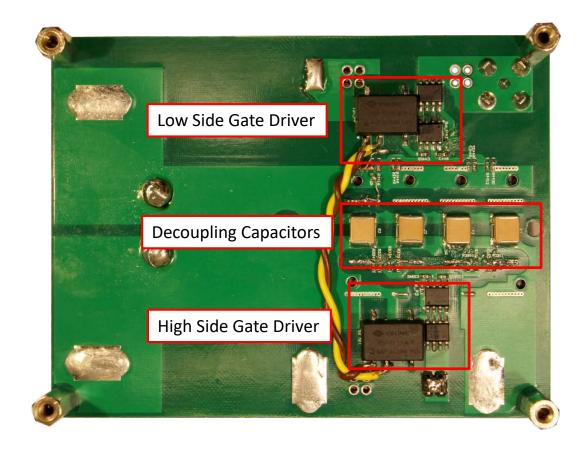

## 4x GS66516T Paralleling Test Board – Bottom View

## Layout of 4x paralleled GaN power stage

# Optimum Paralleling Layout for GaN HEMT (4x GS66516T)

Top side with 4x GS66516T in half bridge

Bot side with gate driver

### Contents

- ☐ Paralleling design considerations

- Layout considerations for paralleling GaN

- Design example of 4x paralleled GaN power stage

- **Experimental results**

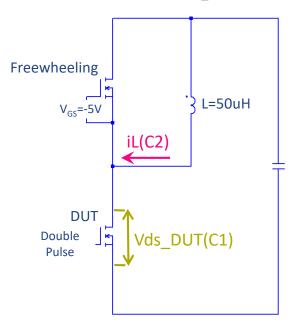

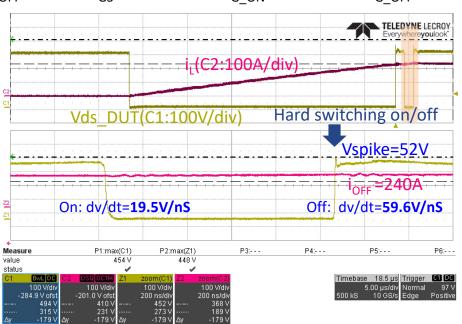

## 400V/240A double pulse hard Switching test waveforms

DUT: 4x GS66516T in parallel; Freewheeling: 4x GS66516T in parallel

Condition:  $V_{BUS}$ =400V,  $I_{DS}$  ON=231A,  $I_{DS}$  OFF=240A,  $V_{GS}$ =+6.8V/-5V,  $R_{G}$  ON=4.550hm,  $R_{G}$  OFF=1.25 ohm.

Measurement Setup: Lecroy WaveSurfer 10M Oscilloscope, HVD3106 Differential Probe(C1), CWT-3LFB mini Rogowski Coil(C2)

**Experimental Waveform**

- No-Derating Paralleling of GaN HEMTs. Hard switched up to full rated current with clean waveform.

- 400V/240A Hard Switching Capability with ~200V V<sub>DS</sub> Margin

## Summary

- Paralleling discrete GaN is desired to achieve higher power output

- GaN Systems E-HEMT device characteristics are inherently fit for paralleling:

- Positive R<sub>DS(ON)</sub> temperature coefficient

- Stable gate threshold over the temperature range

- Negative tempco of g<sub>m</sub>

- Low inductance GaNpx® package for minimum circuit mismatch

- Layout is critical for paralleling high speed GaN HEMT:

- Low and balanced parasitic inductance on the power and gate drive loop. Equal length of gate drive layout and optimum gate driver circuit

- Summary

- Provided practical design guide on how to parallel high speed GaN HEMT devices

- Showed a design layout example of 4x paralleled GaN E-HEMT half bridge power stage

- Hardware was built and GaN E-HEMT paralleled operation has been validated up to the rated current under hard switching test (400V/240A)