GN001 アプリケーションガイドApplication Guide

エンハンスメントモードGaN-HEMTを用いたデザイン

Design with GaN Enhancement mode HEMT

Updated on April 12, 2018 GaN Systems Inc.

※このアプリケーションガイドは「GN001; Design with GaN Enhancement mode HEMT」の日本語に翻訳したものである。

# アプリケーションガイドの概要

- □ 基本特性

- □ ゲートドライブ設計の留意点

- デザイン例

- □ PCB レイアウト

- □ スイッチングテスト結果

弊社の下記リンクより最新情報をご確認ください <a href="http://gansystems.com/design-center/application-notes/">http://gansystems.com/design-center/application-notes/</a>

## GaN HEMTの基礎

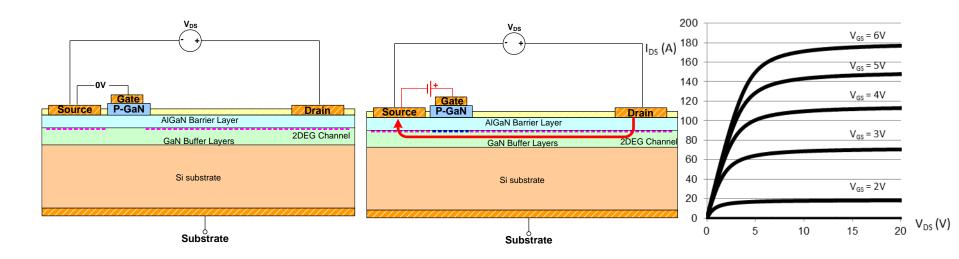

#### GaN エンハンスメント高電子移動度トランジスタ(E-HEMT)

**GaN Enhancement mode High Electron Mobility Transistor**

- 横型AlGaN/GaN ヘテロ エピタキシャル構造により形成される2次元電子ガス(2DEG)は、高電子密度で高速である

- エンハンスメントモードのため、ゲートがOVまたは負バイアスの時 2DEG を枯渇させ、正バイアスの時 2DEGを導通させる

- ゲートの動作は、MOS FETと同様であるが、優れたスイッチング性能を実現する

## E-HEMT ゲート特性

Drain

#### Si MOS FETとの共通点

- エンハンスメントモード(ノーマリーオフ)

- 電圧駆動 Crssの充放電による駆動

- ゲート電流はリーク電流 I<sub>css</sub> のみ

- ゲート抵抗 R<sub>c</sub> により、V<sub>DS</sub>のスルーレートが容易に制御可能

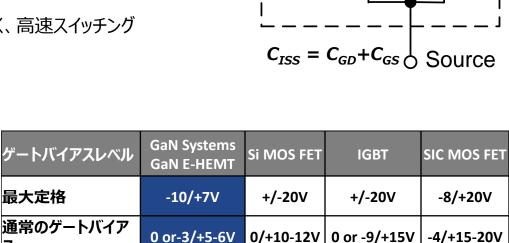

#### Si MOS FETとの相違点

ゲート電荷量(Q<sub>G</sub>)が小さい:ドライブロスが少なく、高速スイッチング

最大定格

- ゲート耐圧が低い V<sub>GS</sub>: 5-6V 推奨値

- ゲート閾値 V<sub>G(th)</sub> が低い: 1.5V (typ)

#### 他のE-HEMTとの比較

- ロバストなゲート: +7/-10V (最大定格)

- ゲートドライブに直流電流は不要

- ゲートにPN接合が無い

R<sub>G,ext</sub> Gate<sub>1</sub> R<sub>G,int</sub>

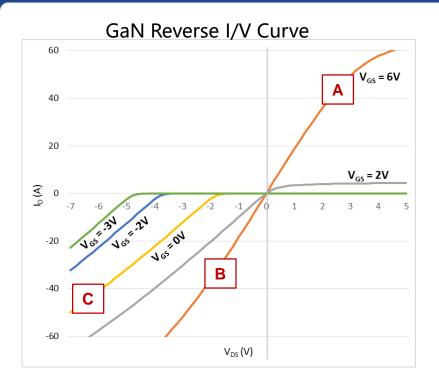

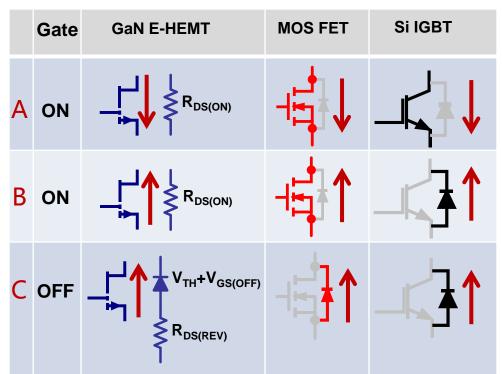

- 2 DEGは第3象限で導通できる 逆並列ダイオードは不要

- ゲートがオフの時 (デッドタイムの期間)、2DEG は  $V_F = V_{th} + V_{GS(off)}$ のダイオードのように動作する デッドタイムロスの低減: 1) デッドタイムを短くする; 2)  $V_{GS(off)}$ は、負バイアスを小さくするか、できれば使わない

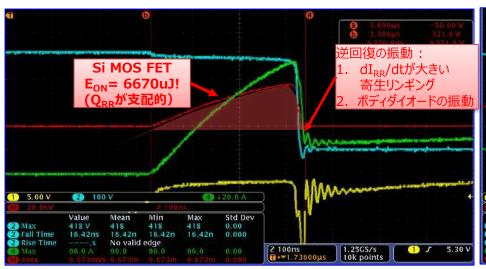

## 逆回復の動作

## 逆回復電荷 Q<sub>RR</sub>:

- GaN は Q<sub>RR</sub> が無いため <u>ハードスイッチングのハーフブリッジ</u> に適している IGBTの置き換え等

- Si MOS FETはハーフブリッジに用いた際、Q<sub>RR</sub>により使用できないハーフブリッジがある

- 逆回復のロスがない GaN は、ブリッジレス トーテムポールのような新しい回路に用いることができる

ハーフブリッジ ターンオン 400V/20A - SJ Si MOS FET

ハーフブリッジ ターンオン 400V/20A - GaN E-HEMT

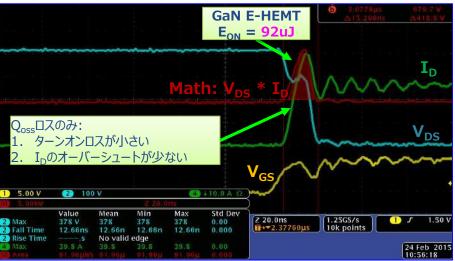

## デッドタイムの設定

## ハードスイッチング用: $t_{d_pwm} > t_{delay\_skew} + (t_{d(off)} - t_{d(on)})$ が必須条件

- R<sub>G</sub>によるターンオン/オフの遅延差は、通常**+/-5ns** の範囲 である(GS66508)

- ハイ/ローサイドのゲートドライバの遅延差は、通常、ワーストケースで決定する。

- ex. Si8261 絶縁ゲートドライバは t<sub>delay\_skew\_max</sub> = **25ns.** このときデッドタイム設定はMin **30ns** 以上必要

- しかし実際の回路は、安全なマージンが必要; GS66508の場合、デッドタイムは、通常 **50-100ns** に選定される

- ソフトスイッチング用のデッドタイムはZVS(ゼロ電圧スイッチング)が成立する値に選定する。

- 100V用GaNのデッドタイムは(**10-20ns**)が用いられる(100V用ドライバが遅延の調整に優れるため)

# アプリケーションガイドの概要

- □ 基本特性

- □ ゲートドライブ設計の留意点

- □ デザイン例

- □ PCB レイアウト

- □ スイッチングテスト結果

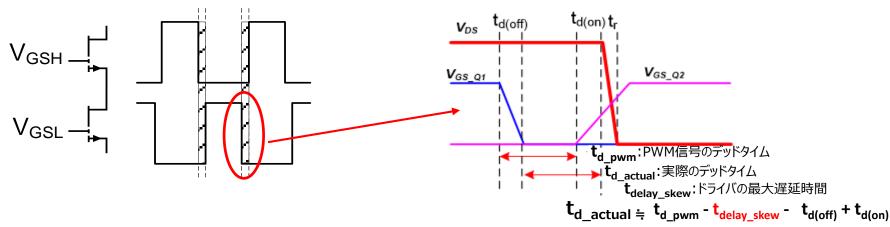

# 設計の留意点 - 高速スイッチング

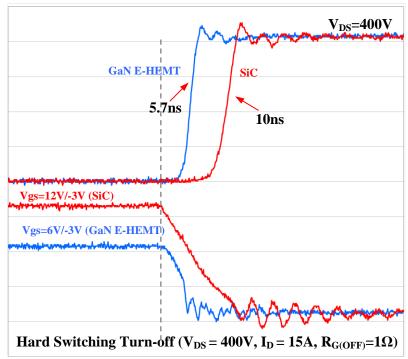

## GaNはSiやSiC MOS FETより高速スイッチング; dv/dt>100V/ns

■ GaNは同程度のオン抵抗のSiC MOS FETに対し、ターンオンが約4倍、ターンオフが約2倍

## 設計の留意点

## GaN E-HEMTの高速スイッチングに対する設計の考慮:

## パワー部からゲートドライブループへのカップリングのノイズの低減をすることが最優先

- 高dv/dt、高di/dt、低C<sub>ISS</sub>、低V<sub>G(th)</sub>の組み合わせ

- ⇒ 安全動作のため、ミラー効果による、ゲート閾値やゲート電圧定格を超える、スパイク電圧を抑える必要がある

- 適切な設計をすることで、ゲート電圧のリンギングを防止し、デバイスの破壊を防ぐ

- GaNの高速のスイッチング性能の実現のため、妥協はすべきでない

- 高dv/dtの発生するハードスイッチングのハーフブリッジに、より重要な考えである

- シングルエンドのトポロジーはミラー効果の影響が少なく、また共振によるゼロ電圧スイッチング(ZVS)は、ハードスイッチングほどの考慮は不要

ここでは、ミラー効果の抑制やゲートのリンギングを低減方法を述べ、推奨のゲートドライバを紹介する

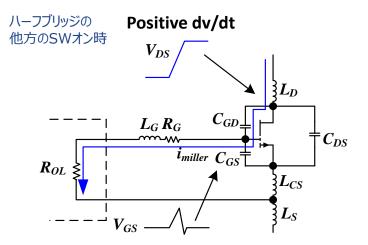

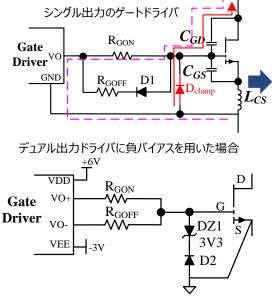

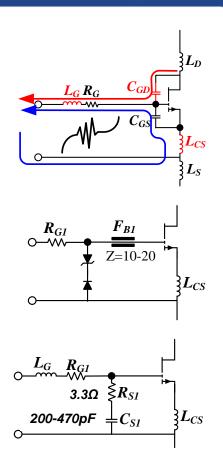

## ミラー効果の抑制

## ゲート回路のインピーダンス (R<sub>G</sub> と L<sub>G</sub>) はターンオンよりターンオフの方が重要

原則; ゲートはできるだけ最小のインピーダンスに抑える必要がある 高dv/dtによるミラー効果の影響は100V用より650V用に顕著に現れる

- 誤動作によるターンオンを防止

- プルダウンの強化 (R<sub>G</sub>/R<sub>OI</sub>を小さくする)

- リンギングを避けるため Loを低減

- ゲートに負バイアスを用いる(推奨値:-2 to -3V)

- ターンオンによるスパイクをV<sub>GS-pk</sub>を-10V以内にする

- プルダウンのためR<sub>G</sub>/R<sub>OL</sub>を低くし、リンギング低減のためL<sub>G</sub>を小さくする

- V<sub>GS</sub> 0V以上の跳ね上がり (LC リンギング); ターンオンの誤動作やゲート発振を防止するためV<sub>G(TH)</sub> 超えさせない

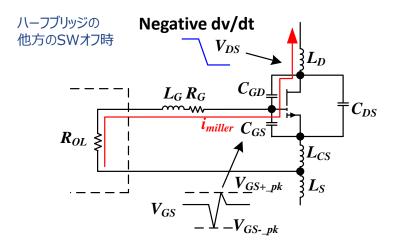

## ミラー効果の抑制

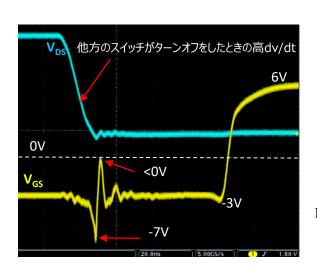

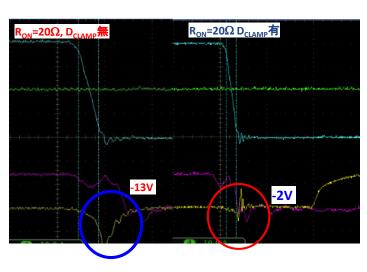

# 負のdv/dt発生時; ミラー効果によるV<sub>GS</sub> スパイク電圧低減のため、低インピーダンス経路の確保が重要 (LC共振によるリンギングを低減する)

- C<sub>tss</sub>/C<sub>rss</sub> の比が変化する V<sub>Ds</sub> < 50 V のV<sub>Gs</sub> のスパイクに注意

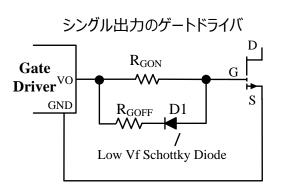

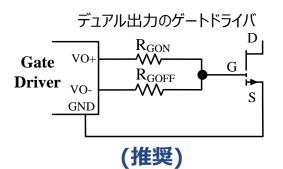

- シングル出力ドライバには、クランプダイオードを推奨(R<sub>GON</sub>大のため)デュアル出力ドライバには不要(ただしR<sub>G</sub>とL<sub>G</sub>による)

- 負のゲートバイアスを用いる場合は、TVS\*ダイオードをクランプダイオードと直列に接続する (互いに逆極性で接続)

- C<sub>GS</sub> の追加は副作用に注意する (L<sub>gate</sub>やL<sub>CS</sub>と LC共振を引き起こす)

- 負のゲートバイアスはターンオンの誤動作を防止するが、最悪の場合でも Vgs-pk > -10Vに抑える

\*TVS (Transient Voltage Suppressor)

## ミラー効果の抑制

#### ゲート抵抗の正しい選定

- GaN E-HEMT のスピードはゲート抵抗により容易に制御できる

- 安定したパフォーマンスと駆動には正しい R<sub>G(ON)</sub>/R<sub>G(OFF)</sub> の比を選択することが重要

- R<sub>G</sub>はターンオンとターンオフとに分けることを推奨

- R<sub>G(ON)</sub>/R<sub>G(OFF)</sub> ≥ 5-10 の割合に選べばミラー効果を抑制可能

- GaN は極めて低い Qg とドライブ損失: 多くの場合 1005/1608サイズのチップ抵抗を使用可能

## ターンオン $R_{G(ON)}$ :

- ターンオンの dv/dt スルーレートを制御

- R<sub>G(ON)</sub> が大きいと dv/dtが遅くなり損失を増大

- R<sub>G (ON)</sub> が小さいと dv/dt が速くなる

- ⇒ ミラー効果によるターンオンやゲートの振動により大きなスイッチング損失になる

- GS66508: R<sub>G(ON)</sub>は10-20Ω の範囲を推奨

## ターンオフ R<sub>G(OFF)</sub>:

- 通常 1-2Ω の範囲を推奨

- ロバストなゲートドライブのために、低抵抗のプルダウンが必要

## ゲートのリンギング/発振の緩和

#### ゲートのリンギングや発振の原因

- ゲートのアンダー/オーバーシュートは L<sub>G</sub> が大きいことが原因

- 共通ソースインインダクタンス L<sub>cs</sub> はパワーループ (di/dt)をゲートループへ返す

- 帰還容量C<sub>GD</sub>による容量結合 (dv/dt)

- 測定用プローブによってもカップリングノイズが発生する

## ゲートのリンギングや発振が発生した場合の対応

- 最初にレイアウトで L<sub>G</sub>, L<sub>CS</sub> と G-D 間のカップリングを低減:

- ドライバはできるだけゲートに接近させて配置

- 太く短い配線でインダクタンスを低減

- ケルビンソース接続を用いて Lccを最小化

- 適切な R<sub>c</sub> を選んで、ターンオンのスルーレートを調整

- ターンオフのため、ゲートに負バイアス (-3V) を試す

- 高周波の LC リンギングやオーバーシュートの抑制の最後の手段:

- フェライトビーズ (Z<sub>0</sub>=10-20Ω@100MHz) をゲートに直列に接続 (フェライトビーズは L<sub>G</sub> を大きくするが、高周波のリンギングを減衰させる)

- RC スナバをG-S間に接続する: 例 R=3.3Ω / C=200-470pF

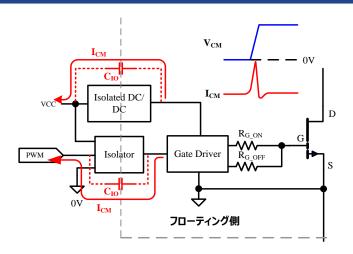

## ハイサイド ドライブの留意点

## GaNはdv/dt>100kV/μsの高速スイッチングを実現:

- 容量結合 C<sub>tO</sub>を最小にする

- C<sub>TO</sub> 介したコモン電流はCMTI\*を制限する

- 絶縁を用いる、またはCMTIの高い絶縁ゲートドライバを用いる CMTI (同相過渡電圧耐性: Common Mode Transient Immunity)

#### ゲートドライブを完全に絶縁:

- 最高のパフォーマンス

- 絶縁の電源供給 内部配線の容量を最小にする

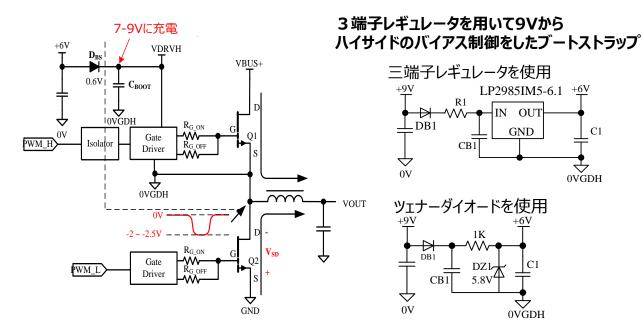

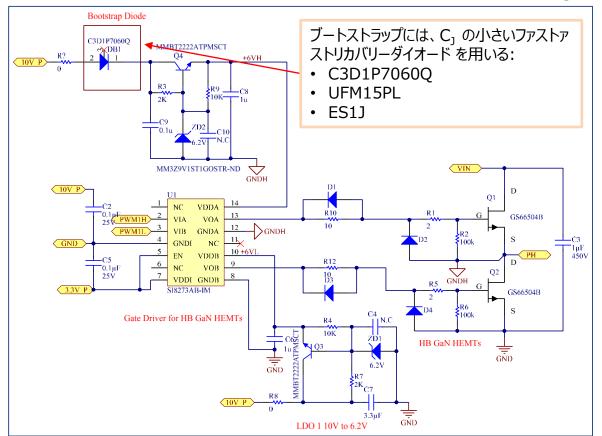

### ブートストラップ:

- 一般に100V用ハーフブリッジの設計に用いられる

- より低コストでシンプルな回路である

- ブーストラップダイオードは、Cjが小さい高速リカバリー品を選び 高周波動作の損失とリカバリー時間を確認する。

- ブートストラップの後にレギュレータや電圧クランプが必要

##

## ブーストストラップ回路

#### 低コストの 0-6V ゲートドライブ

- 従来のブートストラップ回路の問題点

- GaN E-HEMT は高精度のレギュレーションが必要 (定格7Vに対し、5-6Vバイアス)

- ローサイド フリーホイール; 負のノード電圧をコンデンサに過充電する (V<sub>GS</sub>>7V)

- ハイサイド フリーホイール; ブートストラップダイオードの電圧ドロップによりV<sub>cs</sub> が6Vより低くなる

- レギュレータや電圧クランプの使用により、ハイサイドのゲートバイアスを確実に6∨にする

同期整流降圧用のブートストラップ (過充電のクランプだけを行う回路 例:100V同期式降圧コンバータバック)

ツェナーダイオードのみで 6 Vにクランプ

+6V VDRV

DB1 DZ1 C1

5.8V

0VGDH

# **GaN ドライバ/制御 IC の推奨品**

## GaN Systems で検証し 当社GaN E-HEMTs用として推奨されているドライバ:

| Configurations                                                                                                                                        | Gate Driver/Controller IC    |                                                                                       | Design resources |                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------|

| <ol> <li>DC/DC: LLC, PSFB,<br/>Sync Boost/Buck</li> <li>AC/DC: Totem pole<br/>PFC, Active Clamp<br/>Flyback</li> <li>Inverter, motor drive</li> </ol> | SILICON LABS                 | <b>Si8271</b> – Single;<br><b>Si8273/4/5</b> – HB/Dual<br>-GB (0-6V) or –AB (-3/+6V)  |                  | Si827x Datasheet Si8271 demo board (GS66508T) IMS evaluation board User Guide |

|                                                                                                                                                       | ANALOG DEVICES               | ADuM4121ARIZ (0-6V Drive)<br>ADuM4121BRIZ (-3/+6V Drive)                              | PDF              | ADuM4121 Datasheet                                                            |

|                                                                                                                                                       | BROADCOM.                    | ACPL-P346<br>Use -4/+6V gate drive                                                    |                  | ACPL-P346 Datasheet ACPL-P346 Evaluation Board with GS66508T                  |

| <ol> <li>48V DC/DC</li> <li>48V POL</li> <li>Sync. Buck/Boost</li> <li>Class D Audio</li> <li>Wireless Power<br/>Transfer</li> </ol>                  | TEXAS<br>INSTRUMENTS         | <b>LM5113(NRND):</b> 100V, max 5MHz <b>LMG1205:</b> 80V/5A HB Driver                  | PDF              | LM5113 Datasheet<br>LMG1205 Datasheet                                         |

|                                                                                                                                                       | Semi                         | <b>PE29101:</b> 100V, 48V DC/DC, 33MHz <b>PE29102:</b> 60V, Class D Audio, WPT, 40MHz |                  | PE29100 Datasheet PE20102 Datasheet PE29102 Demo board (GS61004B)             |

|                                                                                                                                                       | 力<br>力智電子<br>POWER INTELLECT | UPI Semi GaN FET drivers:<br>uP1966A: Dual-Channel GaN<br>driver                      |                  | uP1966A GaN Driver Ultra High Speed 80V HB Driver for GaN Application         |

# GaNドライバ/制御 IC の推奨品

| Configurations                                                                                                                 | Gate Driver/Controller IC    |                                                                                                                                                                               | Design resources                                                                |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Low side non-isolated driver for 650V/100V GaN*:  1. Flyback, Push-pull 2. Forward 3. Boost PFC 4. Secondary SR 5. Class E P/A | TEXAS<br>INSTRUMENTS         | <b>LM5114/UCC27511:</b> Single Channel, 4A, 5-6V drive <b>UCC27611:</b> w/ internal LDO (5V)                                                                                  | <ul><li><u>■ LM5114 Datasheet</u></li><li><u>■ UCC2751x Datasheet</u></li></ul> |

|                                                                                                                                | 力智電子<br>POWER INTELLECT      | uP1964: Internal LDO for 6V drive                                                                                                                                             | <u>□</u> <u>uP1964 Datasheet</u>                                                |

|                                                                                                                                | Other GaN compatible drivers | IXD609SI: Single, 6V drive, high drive current (9A) FAN3122/TC4422: Single, 6V drive, high drive current (9A) FAN3223/4/5: Dual 4A, 6V drive, for push-pull or SR application |                                                                                 |

| Sync Buck DC/DC (100V GaN):                                                                                                    | ANALOG                       | LTC7800: 60V, Sync. Step-Down<br>Controller (up to 2.2MHz, w/<br>integrated GaN compatible drivers)                                                                           | LTC7800 Datasheet                                                               |

| 1. 48V-12V DC/DC                                                                                                               |                              |                                                                                                                                                                               |                                                                                 |

| Secondary side Rectification (100V GaN):                                                                                       | ON Semiconductor®            | <b>NCP4305A</b> : 5V gate drive clamp, 1MHz max                                                                                                                               | MCP4305 Datasheet                                                               |

| High frequency LLC     Flyback                                                                                                 | life.augmented               | <b>SRK2001:</b> Adaptive SR controller for LLC, 5-6V drive for GaN, 500KHz max                                                                                                | SRK2001 Datasheet                                                               |

[\*]レベルシフト/信号アイソレータと組み合わせることにより、ハイサイドにローサイド非絶縁ドライバを使用できる。

# アプリケーションガイドの概要

- □ 基本特性

- □ ゲートドライブ設計の留意点

- □ デザイン例

- □ PCB レイアウト

- □ スイッチングテスト結果

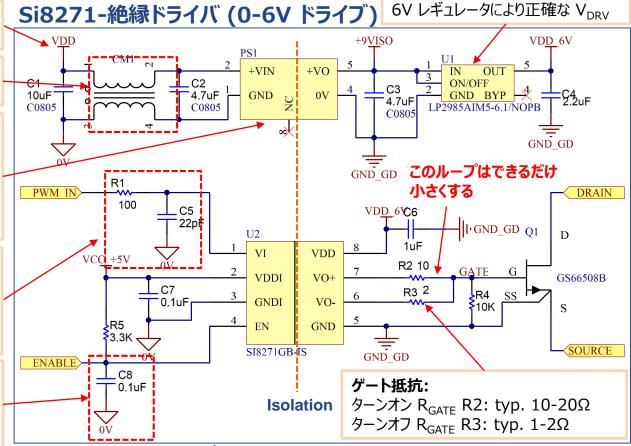

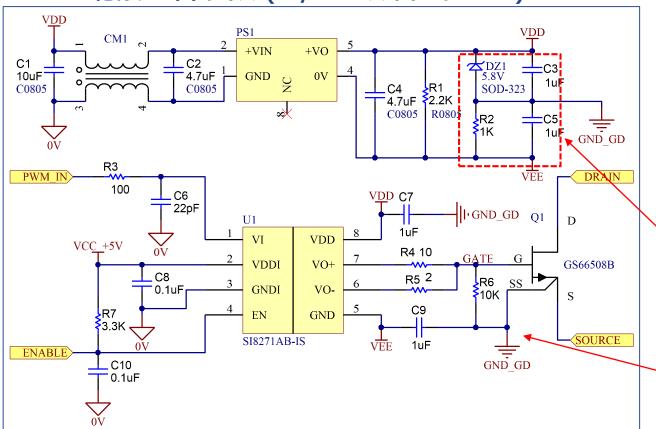

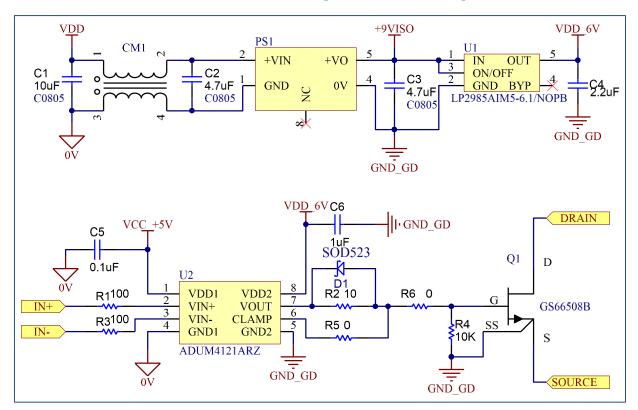

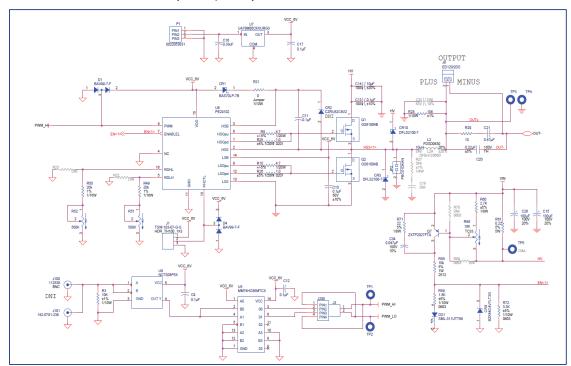

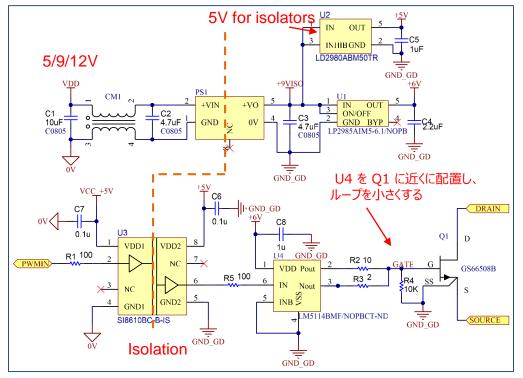

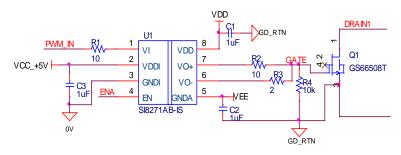

## 650V 絶縁ドライバデザイン #1 - 0-6V ドライブ

VDD: システムの使用電圧に応じて5,9または12V を供給

dv/dtに対するノイズ対策としてコモンモード チョーク追加

#### 絶縁DC/DC電源 PS1の選定:

- VDDより9Vを生成, 1W, 3kV絶縁

- dv/dtの耐性には、低いC<sub>IO</sub> がよい

- 部品型名 参照/推奨:

- RECOM R1S-xx09/HP

- Mornsun Fxx09XT-1WR2

#### PWM 入力:

- コントローラから3.3Vor5Vロジック信号

- ノイズフィルタとしてRCを追加

- ノイズが多い状態では、デグリッチャのある ドライバを検討する (記号 -IS1)

#### **Enable:**

- 未使用時 VDDI に接続

- ENピンの近くにフィルタコンデンサ (100nF)を配置し誤トリガを防止

高周波のZVSのアプリケーションに推奨

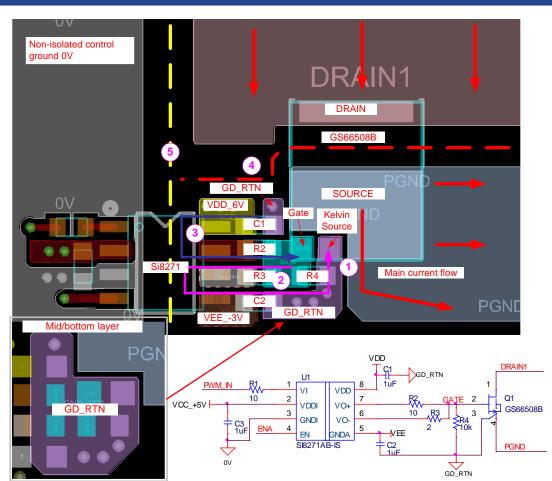

## 650V 絶縁ドライバデザイン #2 - バイポーラドライブ

## Si8271-絶縁ゲートドライバ (-3/+6V バイポーラdrive)

- 貫通やゲート振動を低減し、 速やかにターンオフできる (スインチングロスを低減)

- 逆導通のロスが大きくなる

- ・ ハードスイッチングや高出力の アプリケーションに適する

DZ1 と R2 により 9V を +6V と -3V のゲートバイアスに分ける. 中点はグランドOVとして使用され、GaNデバイスのSS に接続される。

- バイパスコンデンサC7/C9 は U1の VDD/GNDに近づける

- U1 と Q1 Gate/SS はできるだけ近 づける

- 9Vで動かすため、高い UVLO のドライバを使用できる

# ブートストラップ ハーフブリッジ ゲートドライバ

## 低コストの高周波ソフトスイッチングのハーフブリッジ回路に推奨 (AFC;アクティブクランプフライバック, LLC etc)

### LLC テスト波形 (400V/1.3A 600kHz)

# 他の650V ドライバ デザイン リファレンス

## ADuM4121ARZ-GaN HEMT (0-6V ドライブ)用に絶縁ゲートドライバ

# 他の650V ドライバ デザイン リファレンス

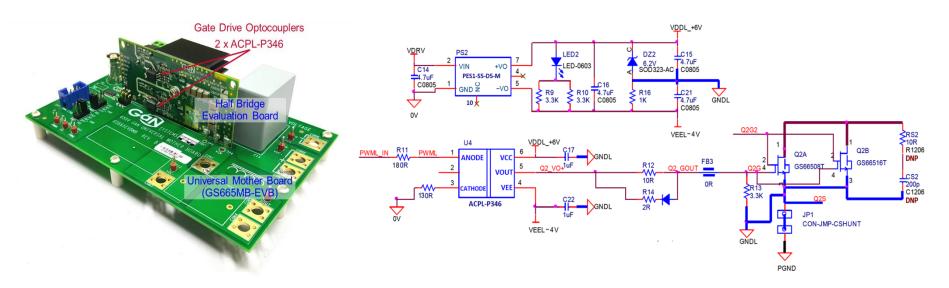

## 絶縁ゲートドライバ; ACPL-P346 (-4/6V)

#### ハーフブリッジ・ボード・リファレンスデザイン

GaN Systems 650V E-HEMT (30A/50m $\Omega$ ) トランジスタ (GS66508T) Broadcom 2.5A フォトカプラのゲートドライブ, ACPL-P346

ドキュメントのダウンロード: https://docs.broadcom.com/docs/ACPL-P346-RefDesign-RM101

# 100V ハーフブリッジGaNドライバ PE29101 Semi

- GaN用 80V HB ドライバ

- 6V ゲートドライブを提供

- 48V DC/DC アプリケーション

- 高周波ドライブ (>5MHz)

- デッドタイム調整可

- 低インダクタンスパッケージ

#### PE29101

http://www.psemi.com/newsroom/new-products/666336-pe29100-gan-fet-driver

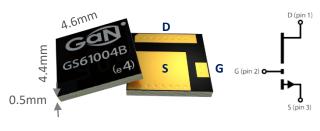

# 100V ハーフブリッジGaNドライバ PE29102 PSemi

## PE29102 - 60V ハーフブリッジ GaN ドライバ, 高周波のアプリケーションに最適化:

D級オーディオアンプ, DC/DC, ワイヤレスチャージング

GS61004B-EVBCD 評価ボードに関する詳細の情報をこちらまで: <a href="http://gansystems.com/design-center/evaluation-boards/">http://gansystems.com/design-center/evaluation-boards/</a>

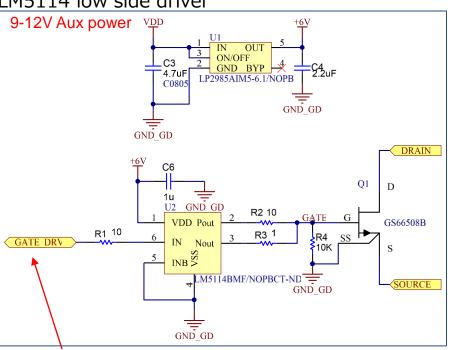

## GaN用 非絶縁ローサイドドライバ

## シングルエンドのアプリケーション (E級電圧共振, フライバック, プッシュプル etc)

• ゲートドライブのバイアスを5-6V でGaNをドライブ (ローサイドまたはハイサイド)

#### LM5114 low side driver

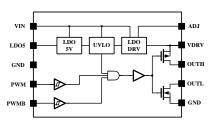

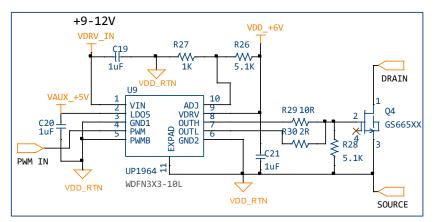

#### **uP1964** GaN ドライバ

- 6 Vバイアスの レギュレータを集積

- 5V 基準電圧出力

制御ロジック信号(3.3/5V) または MOS FET ドライブ出力 (14V以下)

## GaN用 非絶縁ローサイドドライバ

## ハイサイドに絶縁GaNドライバ/ハーフブリッジのローサイドドライバ+シグナルアイソレータ またはHBドライバ

- 従来の絶縁ドライバのソリューションの周波数やドライバ性能の制限を超える

- 既存のコントローラ/ハーフブリッジドライバ を適用(ドライバが高いdv/dtを処理できることを確認)

- ローサイドドライバをGaNに近づけることによってゲートドライブループを改善する

# アプリケーションガイドの概要

- □ 基本特性

- □ ゲートドライブ設計の留意点

- □ デザイン例

- □ PCB レイアウト

- □ スイッチング波形

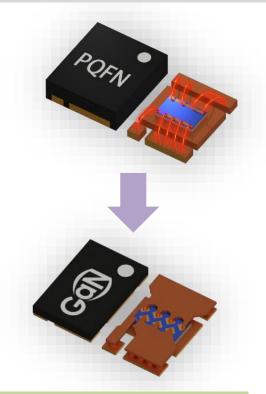

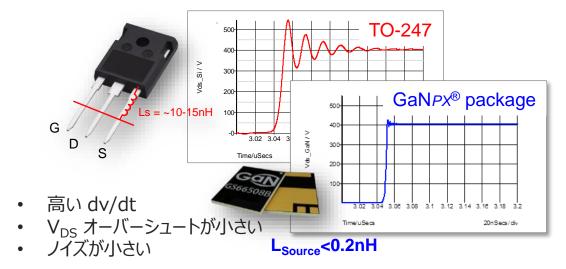

# GaN Systems イノベーション - GaNPX® パッケージング Gan Systems

従来 POFN + ワイヤーバンディング

エンデベッド GaNex® パッケージ

## 高速GaNデバイスのパッケージ イノベーション:

- 超低インダクタンス: 高周波スイッチング

- チップサイズに近いエンデベッドパッケージング

- ワイヤーボンディング無: 高信頼性

- 熱膨張率 C<sub>TE</sub> をPCBに合わせた:温度サイクルの信頼性\*

- 低い熱抵抗 Roc

[\*] GaNpx® パッケージは IPC9701 はんだ接合信頼性試験1000hrを満足する。 条件: 12-Layer 2.5mm PCB, 内部銅箔 175μm, 外部銅箔 70μm

## PCB レイアウトチェックリスト

#### GaNPX® エンベデッドパッケージの設計

- GaNPX® ボトムサイドの放熱 (B/P)

- GaN*px®* トップサイドの放熱 (T)

- 熱設計

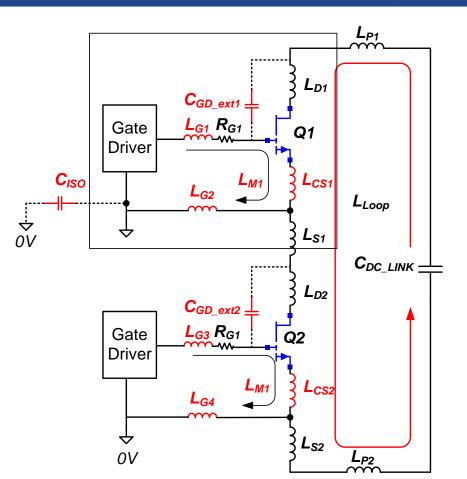

## レイアウトの寄生成分は次の順序で最小化する:

- 1. 共通ソース / 相互インダクタンス L<sub>cs</sub>

- 2. ゲートループインダクタンス  $L_G$

- 3. パワーループインダクタンス L<sub>loop</sub>

- 4. ドレインとゲート間のキャパシタンス CGD ext

- 5. 絶縁カップリングキャパシタンス C<sub>ISO</sub>

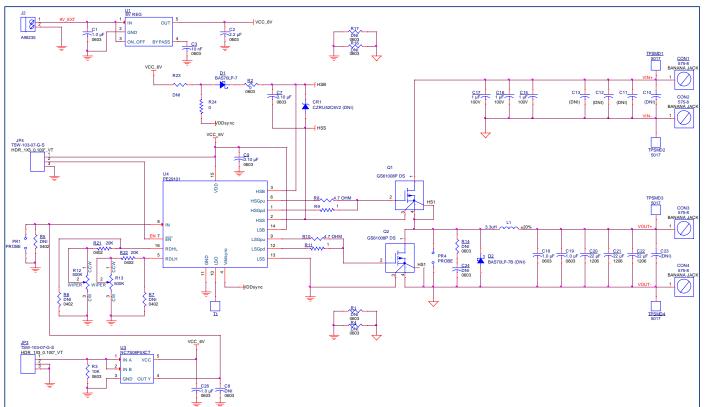

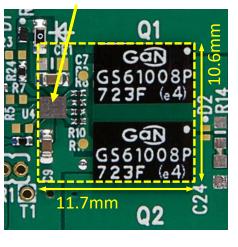

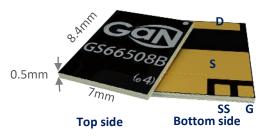

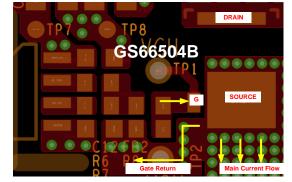

# GaNpx® パッケージ: ボトムサイド放熱 (B タイプ)

- エンベデッドパッケージは究極の低インダクタンス

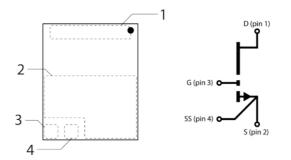

- GS66508B は専用のケルビンソース接続ピン (ソースセンス-SS)がある

- ハイパワー向けには、PCBのビアや金属コアを用いて、PCBに 放熱

#### GS66508B (650V, 30A, $50m\Omega$ )

# GS66504B/GS66502B (650V, 15/7A, 100/200mΩ)

### GS61004B (100V/45A, $15m\Omega$ )

ゲートへのリターンにSSを使う

PCBにケルビンソースをつくる

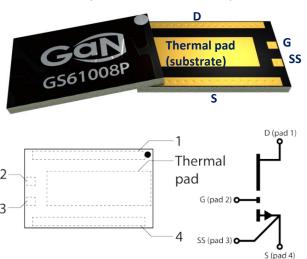

# GaNpx® パッケージ: ボトムサイド放熱 (P タイプ)

- P タイプはサーマルパッドがフローティングであることを除けばB タイプと同じ

- ケルビンソース接続には、SSピンを使う

- サーマルパッドはPCB上でソースに接続することが必須

#### GS61008P (100V/90A, $7.5m\Omega$ )

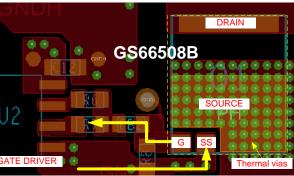

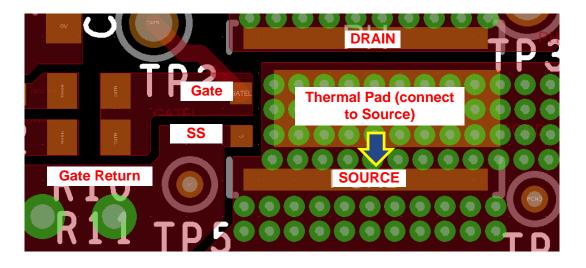

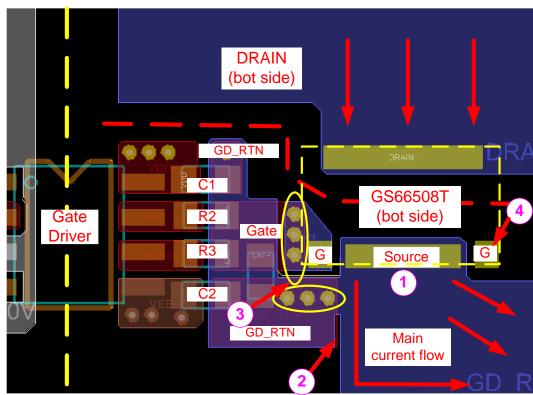

# 最適なレイアウト例 ーボトムサイド放熱のゲートドライブ

- 1 ドライブとパワーGNDを分離するためケルビン ソースを使う/つくる (低いL<sub>CS</sub>).ノイズを小さく するため、高電流ループとドライブループを物理 的に分離する

- プルダウンのループを最小化する (Gate→R3 → U1 → C2 →GS\_リター ン, U1 と C2 を近づけ配置)

- ③ ターンオン(プルアップ)のループを最小化する (C1 を近づけ配置)

- 4 ゲートドライブとドレインパターンの間を絶縁 しオーバーラップを避ける

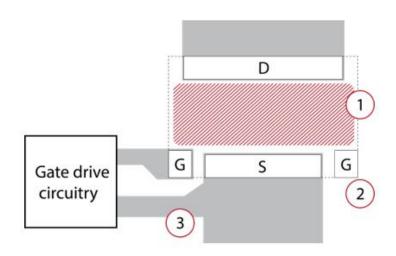

# 最適なレイアウト例 - トップサイド放熱のゲートドライブ

- ① GaNPX® T タイプのドライブは、ヒートシンクの 取り付けのため、裏面にレイアウトする

- (2) ゲートドライブのリターンヘケルビンソース接続をつくる (裏面側)

- 3 複数のビアを使って裏面から表面へのインダク タンスを低くする

- ダートピンは一つを使い、もう一つは接続しない

# 最適なレイアウト例 ートップサイド放熱のゲートドライブ

- ① このエリアには配線しない:直接、トップサイド放熱パッケージの下のPCBのトップレイヤーにパターンやビアを配置することを避ける。これは、高い温度と高電圧の動作中のマイグレーションやソルダーマスクの絶縁劣化問題を防ぐためである

- ② 対称の2つのゲートはフレキシブルなレイアウトと容易な並列動作のためにある。どちらも使うことができるが、使わない方は、フローティングにする

- ③ トップサイド放熱のタイプには、ソースセンス(SS)はない。これは 超低インダクタンスの GaNPx® のパッケージを実現するためで ある。ソースセンスはゲート端子近傍のソースパッドから信号を引き出すことで機能させることができる。これにより、どちらかのソース パッドの横でレイアウトの最適化を行うことができる

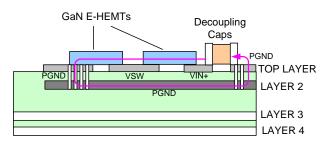

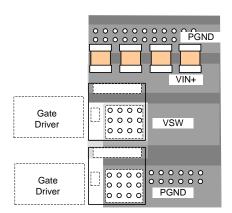

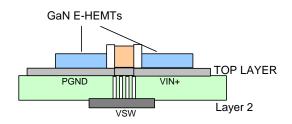

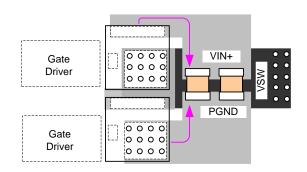

# 最適なレイアウト例 - ハーフブリッジのパワー部

## 小さいループと低いインダクタンスのハーフブリッジのパワー部の設計

#### ハーフブリッジの設計 1

2番目の層をグランドリターンに使う(4層PCB) トップレイヤーをパワーループのみに使う

## ハーフブリッジの設計 2

## レイアウトガイダンス

- 4層のPCBを推奨する

- 2番目の層をグランドにする

- 面実装のセラミックコンデンサを デカップリングコンデンサに用い て、GaNに近づけて配置する

- 複数のコンデンサを用いて ESR/ESLを低減し、安定した パワーループをつくる

- ドライバはゲートに近づける

- ドライブのリターンにケルビンソー スを用いる

# アプリケーションガイドの概要

- □ 基本特性

- □ ゲートドライブ設計の留意点

- □ デザイン例

- □ PCB レイアウト

- □ スイッチングテスト結果

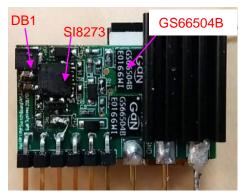

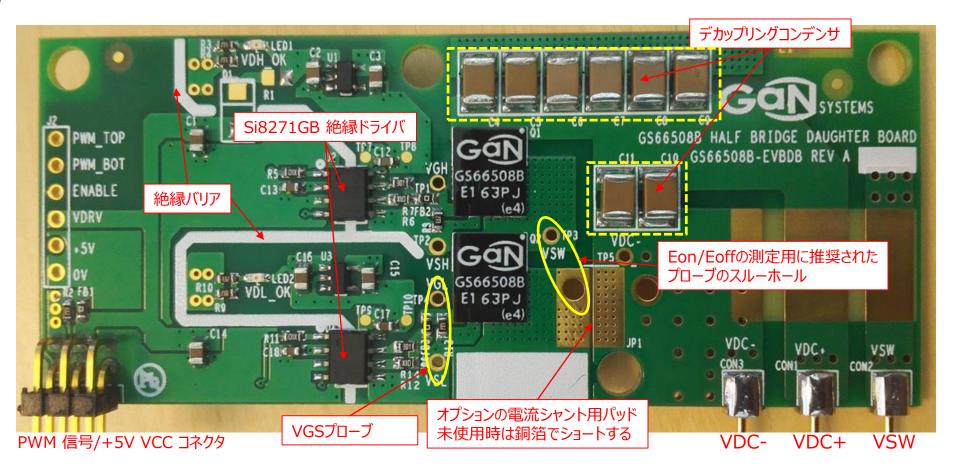

# スイッチングテスト - GS66508B ハーフブリッジ評価ボード GQN

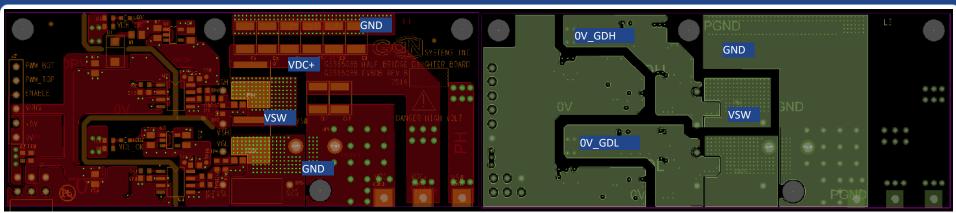

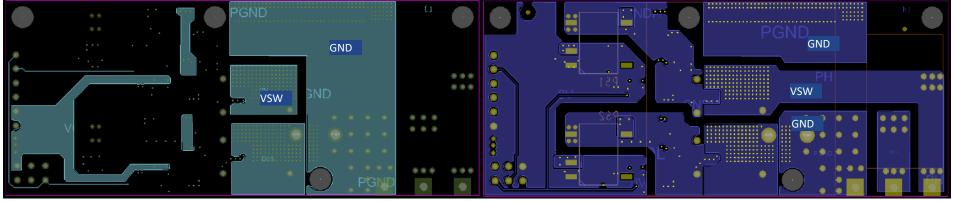

# GS66508B-EVBDB PCBのレイアウト

Top Layer

Mid layer 1

Mid layer 2

**Bottom Layer**

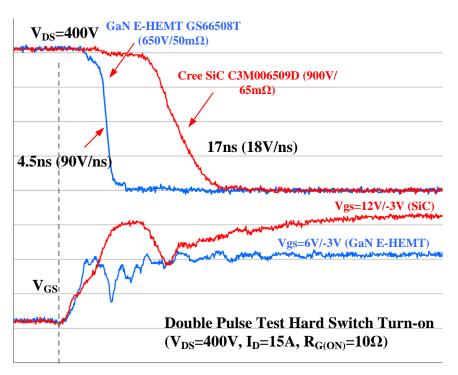

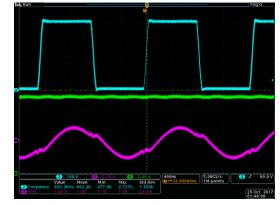

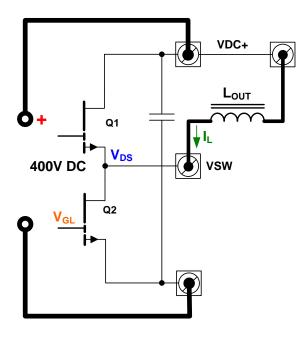

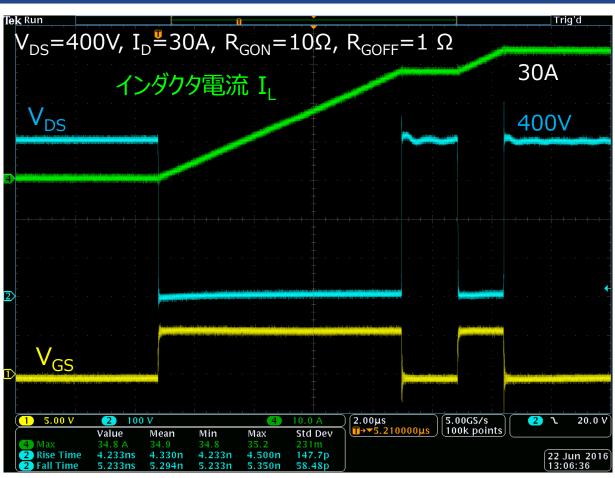

# GS66508 ダブルパルス スイッチングテスト

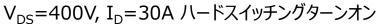

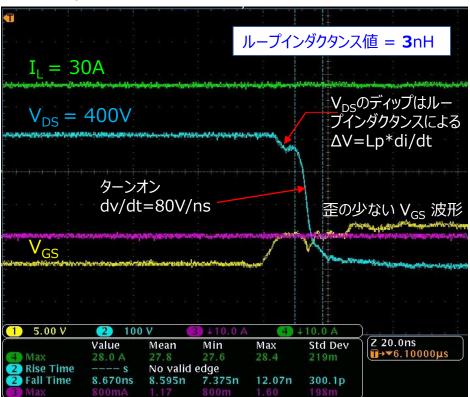

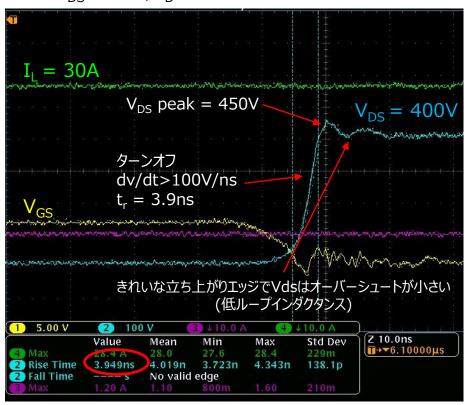

■ GS66508B ハードスイッチンッグ(400V/30A)

# GS66508 ダブルパルス スイッチングテスト (拡大)

### $V_{DS}$ =400V, $I_{D}$ =30A ハードスイッチングターンオフ

- このアプリケーションガイドで、GaN Systems の GaN E-HEMTs を用いる時の重要な設計の留意点をまとめた。 GaN E-HEMTの基礎から、ゲートドライブ設計の検討事項までを述べた

- また、推奨ドライバのリストと様々なゲートドライブのリファレンスデザインについても提供した

- 実際にハーフブリッジ評価ボードを作成し、そのスイッチング性能をテストした

- 400V/30Aのスイッチング試験結果は、リンギングやオーバーシュートが抑制され、高速かつクリーンなハードスイッチング波形を示した。これは、低インダクタンスの GaNpx®のパッケージを用いて、最適なゲートドライブと基板レイアウト設計を行うことで、GaN E-HEMTの性能を最大限に引き出せることを示している

# デザインリソース

● データシート,スパイスモデル

Datasheets, spice models: <a href="http://www.gansystems.com/transistors.php">http://www.gansystems.com/transistors.php</a>

● 評価ボード

Evaluation boards: <a href="http://www.gansystems.com/eval-boards.php">http://www.gansystems.com/eval-boards.php</a>

● アフ°リケーションノート

Application notes: <a href="http://gansystems.com/design-center/application-notes/">http://gansystems.com/design-center/application-notes/</a>

● PCB プットプリントライプラリー

PCB Footprint libraries: <a href="http://www.gansystems.com/transistors.php">http://www.gansystems.com/transistors.php</a>

● よくある質問

FAQ: <a href="http://gansystems.com/gan-transistors/faq/">http://gansystems.com/gan-transistors/faq/</a>

● 論文,プレゼンテーション資料

Papers and Presentations: <a href="http://gansystems.com/design-center/papers/">http://gansystems.com/design-center/papers/</a>

# Tomorrow's power today™